MANCHESTER METROPOLITAN UNIVERSITY

BSc. (HONS) COMPUTER SCIENCE

---

## An Investigation into Value Profiling and its Applications

---

*Author:*

Graham MARKALL

*Supervisor:*

Dr. Andy NISBET

No part of this project has been submitted in support of an application for any other degree or qualification at this or any other institute of learning. Apart from those parts of the project containing citations to the work of others, this project is my own unaided work.

Signed -----

## Abstract

Value Profiling is the recording of live inputs and outputs of computations during the execution of a program. Value Profiling can be used to determine the invariance of the inputs and outputs of these computations. Computations with high degrees of invariance in their inputs may be the subject of optimisations to exploit this behaviour. Previous research into Value Profiling has shown that there is a significant amount of invariance in the inputs of computations throughout the execution of most programs that cannot be detected at compile-time. Other research efforts have used Value Profile data to guide the design of schemes to increase performance or decrease power consumption. This project seeks to validate the hypothesis that there is a high level of invariance in the inputs of computations throughout the execution of most programs. Value Profiling tools were developed on two different platforms and used to record Value Profile data. The recorded Value Profile data is examined, and it is shown that there are high levels of invariance in the inputs of computations throughout the execution of most programs. Additionally the Value Profile data was used to guide the design of a bus encoding to reduce power consumption by the memory bus, and to develop a cache (termed a *Value Reuse Cache*) which stores and recalls the live inputs and outputs of frequently occurring computations to improve performance. Both of these schemes are promising - the Value Reuse Cache is shown to have an average hit rate of over 60% for all cacheable instructions across all benchmarks, and the bus encoding reduces switching activity by over 40% in certain cases.

# Acknowledgements

People who have contributed to this project and I would like to thank are:

- Dr. Andy Nisbet, for his supervision of this project, and providing me with guidance and suggestions throughout.

- The technicians in the Department of Computing and Mathematics, who assisted by setting up a machine with plenty of RAM and extra disk space to use for Value Profiling runs.

- Sarah Burberry, for finding me quiet places to work on this report.

# Contents

|          |                                                                                                                     |           |

|----------|---------------------------------------------------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                                                                                 | <b>1</b>  |

| 1.1      | What is Value Profiling? . . . . .                                                                                  | 1         |

| 1.2      | Why use Value Profiling? . . . . .                                                                                  | 1         |

| 1.3      | The Low-Level Virtual Machine Compiler Infrastructure . . . . .                                                     | 2         |

| 1.4      | Pin . . . . .                                                                                                       | 3         |

| 1.5      | MiBench Benchmarks/MiDataSets . . . . .                                                                             | 4         |

| 1.6      | Conclusion to Introduction . . . . .                                                                                | 4         |

| <b>2</b> | <b>Literature Review</b>                                                                                            | <b>5</b>  |

| 2.1      | Introduction . . . . .                                                                                              | 5         |

| 2.2      | Value Profiling . . . . .                                                                                           | 5         |

| 2.3      | Dynamic Instruction Reuse . . . . .                                                                                 | 6         |

| 2.4      | An Analysis of the Potential for Global Level Value Reuse in the SPEC95 and SPEC2000 Benchmarks . . . . .           | 7         |

| 2.5      | Frequent Value Locality and its Applications . . . . .                                                              | 7         |

| 2.6      | Increasing Instruction-Level Parallelism with Instruction Precomputation . . . . .                                  | 9         |

| 2.7      | Value Reuse Optimization: Reuse of Evaluated Math Library Function Calls Through Compiler Generated Cache . . . . . | 10        |

| 2.8      | Exploiting Frequent Field Values in Java Objects for Reducing Heap Memory Requirements                              | 11        |

| 2.9      | Review . . . . .                                                                                                    | 12        |

| <b>3</b> | <b>Areas of investigation &amp; Hypotheses</b>                                                                      | <b>13</b> |

| 3.1      | Summary . . . . .                                                                                                   | 13        |

| 3.2      | Analysing the Usage and Effects of the GETELEMENTPTR Instruction . . . . .                                          | 14        |

| 3.2.1    | Allocation of Storage Space . . . . .                                                                               | 14        |

| 3.2.2    | Introducing the GETELEMENTPTR Instruction . . . . .                                                                 | 14        |

| 3.2.3    | Compilation of the GETELEMENTPTR Instruction . . . . .                                                              | 15        |

| 3.2.4    | Use of the GEP Instruction in the MiBench Benchmarks . . . . .                                                      | 17        |

| 3.2.5    | Observations . . . . .                                                                                              | 17        |

| 3.3      | Hypotheses . . . . .                                                                                                | 18        |

| 3.4      | Methods of investigation . . . . .                                                                                  | 18        |

| <b>4</b> | <b>Implementation</b>                                                                                               | <b>20</b> |

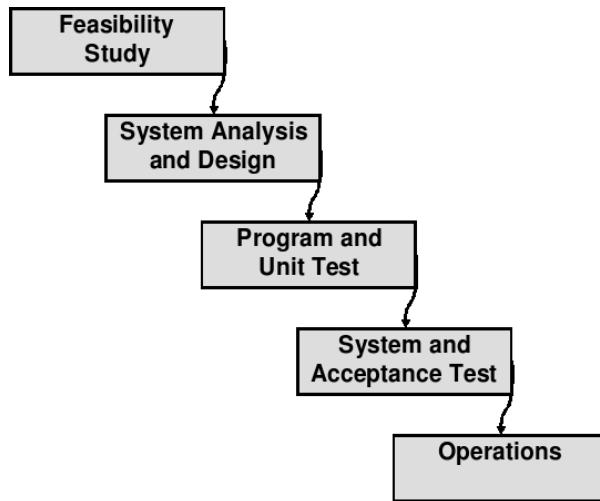

| 4.1      | Development methodology - The Waterfall Lifecycle . . . . .                                                         | 20        |

| 4.2      | Feasibility Study . . . . .                                                                                         | 22        |

| 4.2.1    | Technical Feasibility . . . . .                                                                                     | 22        |

| 4.2.2    | An outline of the systems . . . . .                                                                                 | 22        |

| 4.2.3    | Required Hardware/Software . . . . .                                                                                | 23        |

| 4.3      | System Analysis & Design . . . . .                                                                                  | 23        |

| 4.3.1    | Requirements Analysis for Value Profiling of Computations at the Instruction Level                                  | 23        |

| 4.3.2    | Choosing instructions of the LLVM IR to profile . . . . .                                                           | 23        |

| 4.3.3    | Choosing x86 Instructions to Profile . . . . .                                                                      | 24        |

| 4.3.4    | Additional attributes to record - LLVM & x86 implementations . . . . .                                              | 26        |

| 4.3.5    | Requirements Analysis for Value Profiling of Memory Accesses . . . . .                                              | 26        |

|          |                                                                                           |            |

|----------|-------------------------------------------------------------------------------------------|------------|

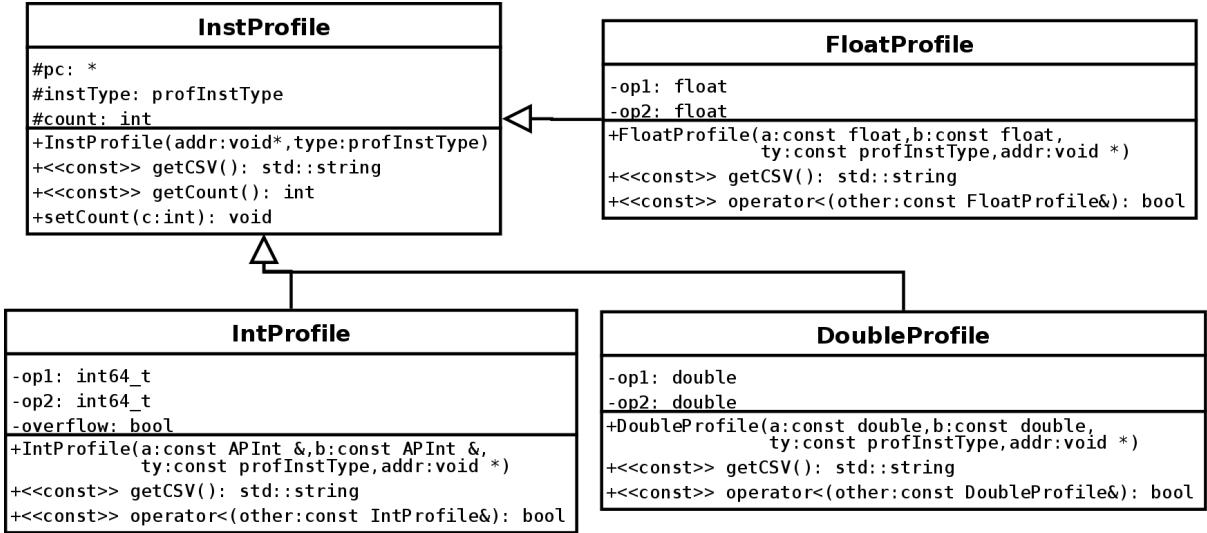

| 4.3.6    | A Design of Classes to Record Value Profile Data . . . . .                                | 26         |

| 4.3.7    | Inserting Instrumentation Code on LLVM . . . . .                                          | 30         |

| 4.3.8    | Inserting Instrumentation Code on the x86 Architecture . . . . .                          | 32         |

| 4.4      | Program & Unit Test . . . . .                                                             | 35         |

| 4.5      | System & Acceptance Test . . . . .                                                        | 36         |

| 4.5.1    | Global-level Instruction Profiling on LLVM . . . . .                                      | 36         |

| 4.5.2    | Global-level Memory Profiling on LLVM . . . . .                                           | 37         |

| 4.5.3    | Local-level Memory Profiling on LLVM . . . . .                                            | 39         |

| 4.5.4    | Global-level Instruction Profiling on the x86 Architecture . . . . .                      | 41         |

| 4.5.5    | Global-level Memory Profiling on the x86 Architecture . . . . .                           | 42         |

| 4.5.6    | Local-level Memory Value Profiling on the x86 Architecture . . . . .                      | 44         |

| 4.6      | Operations . . . . .                                                                      | 47         |

| 4.7      | Modification of the LLVM Interpreter to call library functions required by the benchmarks | 47         |

| 4.7.1    | Calling external functions through wrapper functions . . . . .                            | 47         |

| 4.7.2    | Anatomy of a wrapper function . . . . .                                                   | 48         |

| 4.7.3    | Choosing the correct functions to implement . . . . .                                     | 48         |

| 4.8      | Post-Processing of Instruction Level Value Profile Data . . . . .                         | 50         |

| 4.8.1    | Sorting and Mathematical Operations . . . . .                                             | 50         |

| 4.8.2    | Presenting the Output . . . . .                                                           | 52         |

| 4.9      | Conclusion to Implementation . . . . .                                                    | 52         |

| <b>5</b> | <b>Results &amp; Analysis</b>                                                             | <b>53</b>  |

| 5.1      | LLVM Value Profile Data . . . . .                                                         | 53         |

| 5.1.1    | Global-level Instruction Value Profiling . . . . .                                        | 53         |

| 5.1.2    | Global-level Memory Access Value Profiling . . . . .                                      | 65         |

| 5.1.3    | Local-Level Memory Access Value Profiling . . . . .                                       | 75         |

| 5.2      | X86 Architecture (Pin) Value Profile Data . . . . .                                       | 77         |

| 5.2.1    | Global-Level Instruction Value Profiling . . . . .                                        | 77         |

| 5.2.2    | Global-level Memory Value Profiling . . . . .                                             | 85         |

| 5.2.3    | Local-level Memory Access Value Profiling . . . . .                                       | 94         |

| 5.3      | Conclusion to the Results and Analysis . . . . .                                          | 94         |

| <b>6</b> | <b>Exploiting Value Reuse in Instruction Executions - A Value Reuse Cache</b>             | <b>96</b>  |

| 6.1      | Background . . . . .                                                                      | 96         |

| 6.2      | Design of the Value Reuse Cache . . . . .                                                 | 96         |

| 6.3      | Implementation of the Value Reuse Cache . . . . .                                         | 97         |

| 6.4      | Testing the Value Reuse Cache . . . . .                                                   | 98         |

| 6.5      | Results & Effects of the Value Reuse Cache . . . . .                                      | 102        |

| 6.5.1    | Global-Level Value Reuse Cache . . . . .                                                  | 102        |

| 6.5.2    | A comparison across all benchmarks . . . . .                                              | 109        |

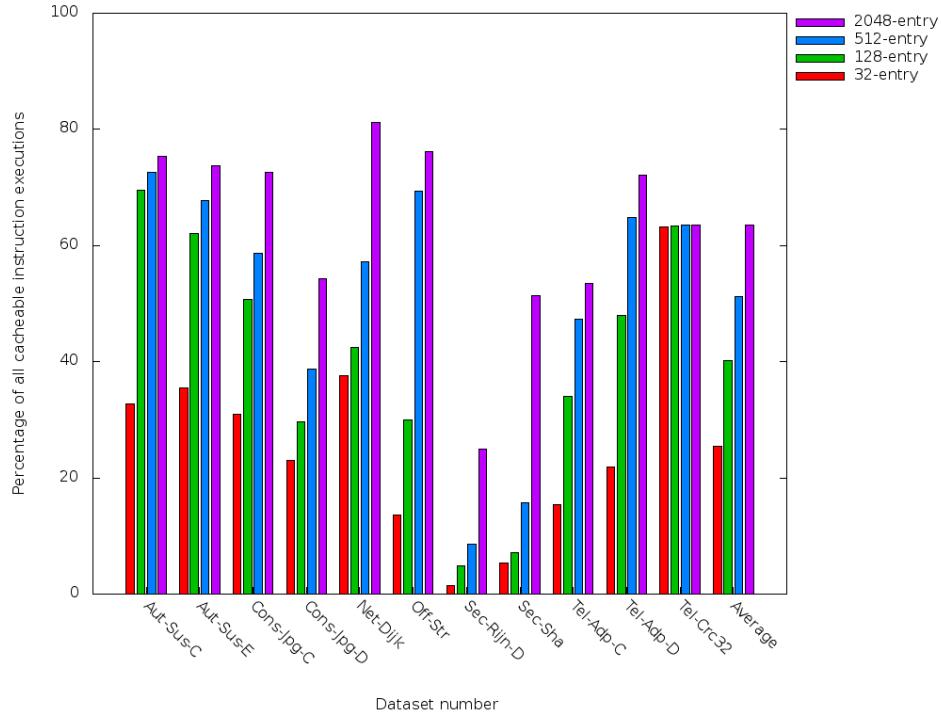

| 6.5.3    | Considering Only Cacheable Instruction Executions . . . . .                               | 111        |

| 6.5.4    | Local-level Value Reuse Cache . . . . .                                                   | 112        |

| 6.6      | Conclusion . . . . .                                                                      | 120        |

| <b>7</b> | <b>A More Representative Memory Access Value Profile - Using a Cache Simulator</b>        | <b>121</b> |

| 7.1      | Background . . . . .                                                                      | 121        |

| 7.2      | A Pin Tool to Simulate a Cache . . . . .                                                  | 121        |

| 7.3      | Insertion of Instrumentation Code . . . . .                                               | 123        |

| 7.4      | Testing . . . . .                                                                         | 123        |

| 7.5      | Results . . . . .                                                                         | 123        |

| 7.5.1    | A Comparison Across all Benchmarks . . . . .                                              | 130        |

| 7.6      | Reducing Power Consumption by Exploiting the Effect of a Cache . . . . .                  | 132        |

| 7.6.1    | The Scheme . . . . .                                                                      | 132        |

| 7.6.2    | Example Operation of the Scheme . . . . .                                                 | 133        |

| 7.6.3    | Testing of the Scheme . . . . .                                                           | 134        |

| 7.7      | Conclusion . . . . .                                                                      | 135        |

|                                                                                |            |

|--------------------------------------------------------------------------------|------------|

| <b>8 Conclusions</b>                                                           | <b>136</b> |

| 8.1 Hypothesis 1                                                               | 136        |

| 8.2 Hypothesis 2                                                               | 136        |

| 8.3 Hypothesis 3                                                               | 136        |

| 8.4 Hypothesis 4                                                               | 136        |

| 8.5 Hypothesis 5                                                               | 136        |

| 8.6 Hypothesis 6                                                               | 137        |

| 8.7 Hypothesis 7                                                               | 137        |

| <b>9 Evaluation</b>                                                            | <b>138</b> |

| 9.1 Evaluation of Pin and LLVM as Platforms for Value Profiling                | 138        |

| 9.2 Evaluation of the Execution of the Project                                 | 139        |

| 9.2.1 Learning C++                                                             | 139        |

| 9.2.2 A Lack of Support for External Library Functions in the LLVM Interpreter | 140        |

| 9.2.3 Removal of Basic-Block Value Profiling from Aims and Objectives          | 140        |

| 9.2.4 Introduction of Pin as a Platform for Value Profiling                    | 140        |

| 9.3 Conclusion                                                                 | 140        |

| <b>10 Further work</b>                                                         | <b>141</b> |

| 10.1 Investigation into Precomputation Tables                                  | 141        |

| 10.2 Examination of the Distribution of Frequent Values in Memory              | 142        |

| 10.3 Testing the Memory Bus Power Reduction Scheme                             | 142        |

| 10.4 Refinement of the Value Reuse Cache                                       | 142        |

| <b>Appendices</b>                                                              | <b>144</b> |

| <b>A Terms of Reference</b>                                                    | <b>144</b> |

| A.1 Project Background                                                         | 144        |

| A.2 Aims                                                                       | 144        |

| A.3 Objectives                                                                 | 144        |

| A.4 Deliverables                                                               | 145        |

| A.5 Resources                                                                  | 145        |

| <b>B Test Cases</b>                                                            | <b>146</b> |

| <b>C CD Contents</b>                                                           | <b>151</b> |

| C.1 Report and JISC Originality Report                                         | 151        |

| C.2 Value Profiling Tools                                                      | 151        |

| C.2.1 LLVM                                                                     | 151        |

| C.2.2 Pin                                                                      | 151        |

| C.3 Test cases                                                                 | 152        |

| C.4 Value Profile Data                                                         | 152        |

| C.4.1 LLVM Value Profile Data                                                  | 153        |

| C.4.2 Pin Value Profile Data                                                   | 153        |

| C.5 MiBench Benchmarks and Midatasets Datasets                                 | 153        |

| <b>References</b>                                                              | <b>154</b> |

# List of Figures

|      |                                                                                                                                                                                 |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1  | The stages of the LLVM compilation process from C and C++.                                                                                                                      | 2  |

| 1.2  | The architecture of Pin.                                                                                                                                                        | 3  |

| 4.1  | The Waterfall Lifecycle.                                                                                                                                                        | 20 |

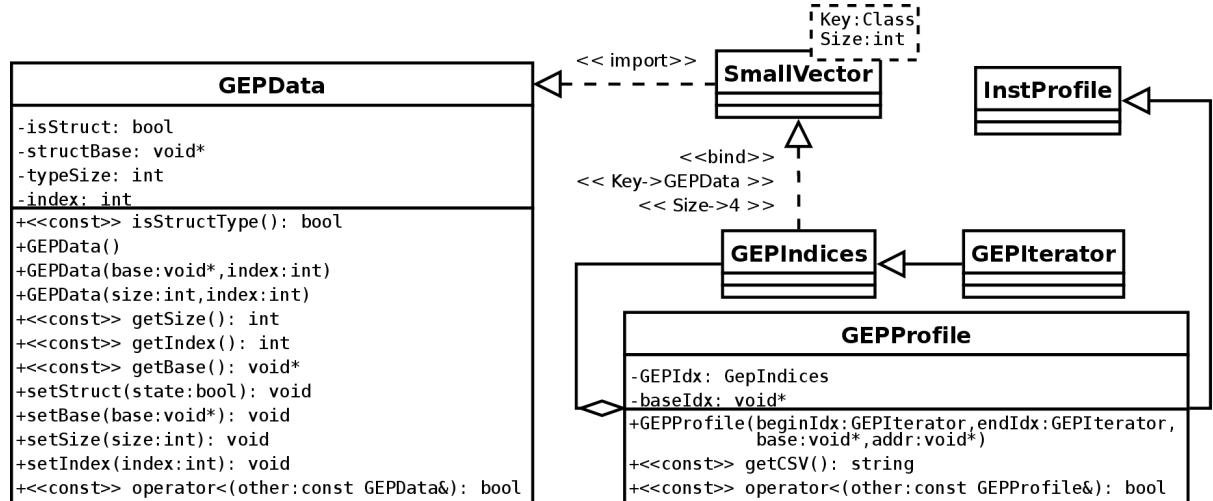

| 4.2  | InstProfile class and subclasses to profile all Binary Operations using LLVM.                                                                                                   | 27 |

| 4.3  | Classes involved in profiling the GEP instruction using LLVM.                                                                                                                   | 27 |

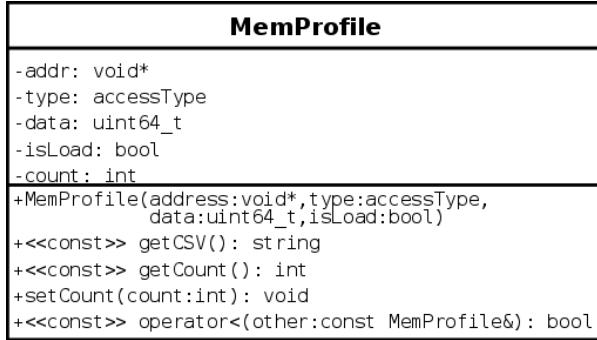

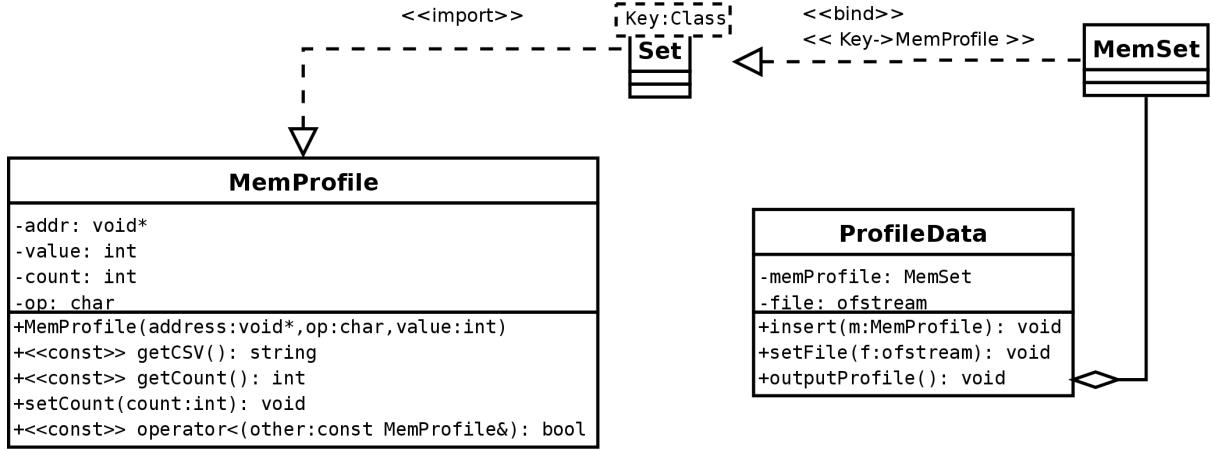

| 4.4  | The MemProfile class for Value Profiling Memory Accesses using LLVM.                                                                                                            | 28 |

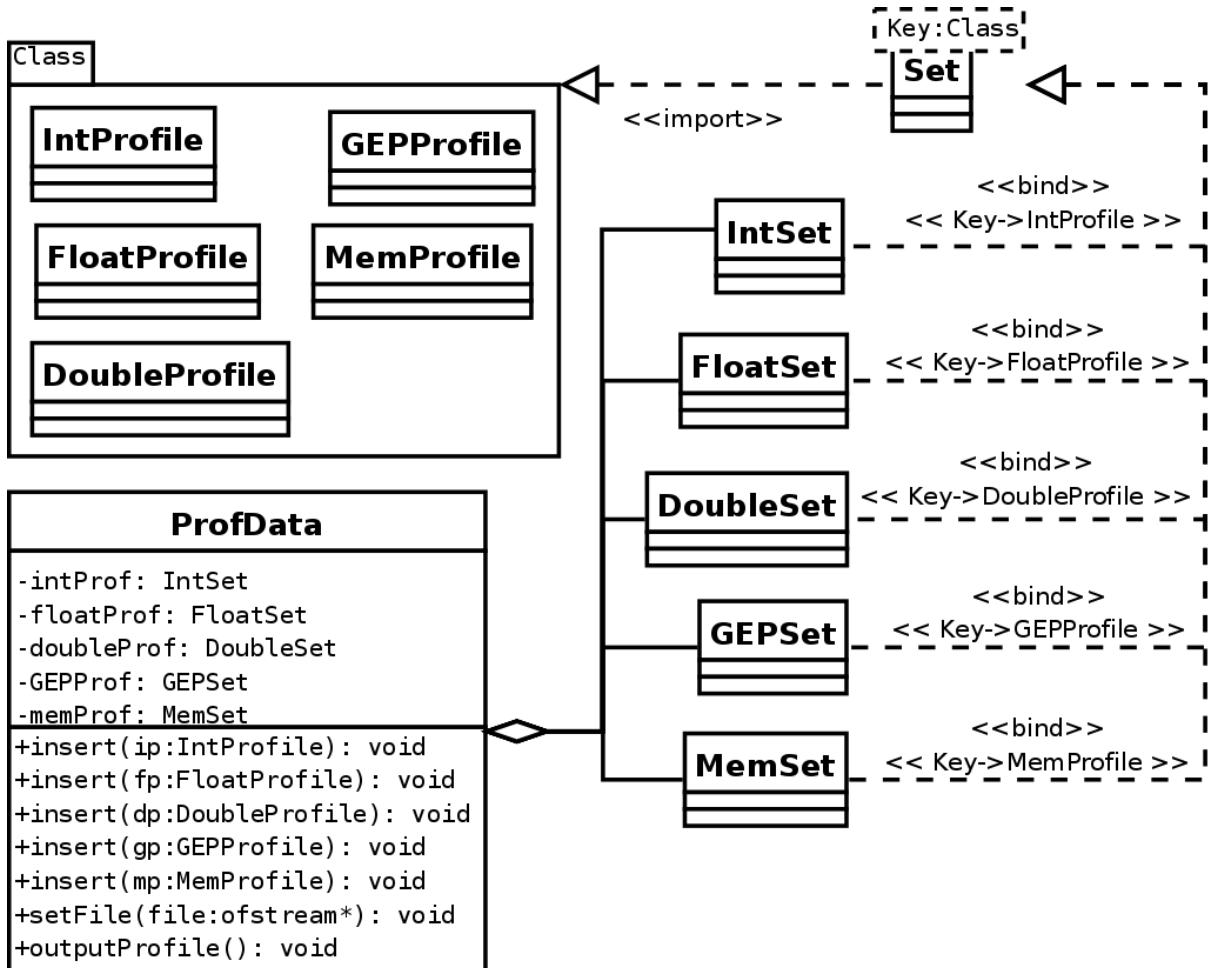

| 4.5  | The ProfData class and STL sets of profiling classes used with LLVM.                                                                                                            | 29 |

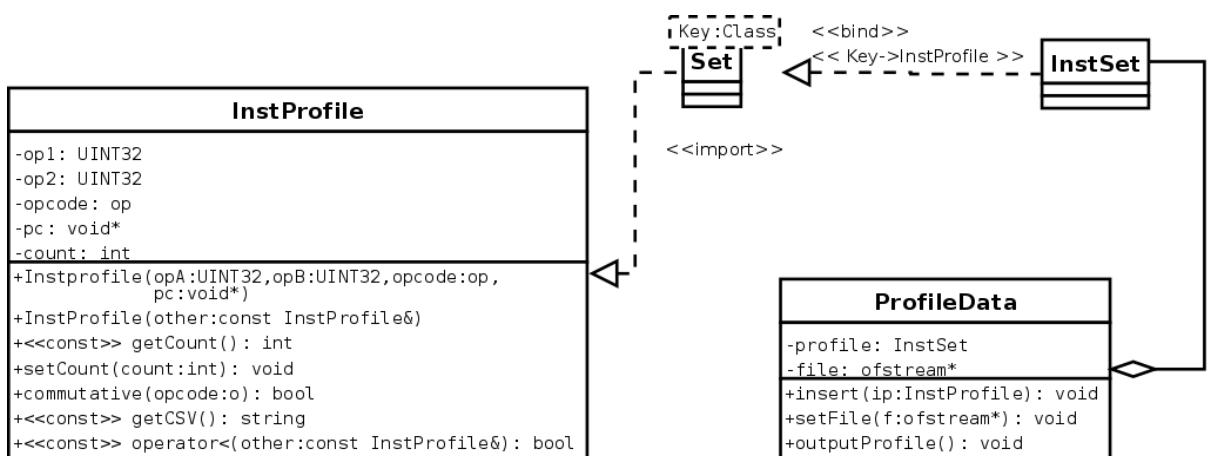

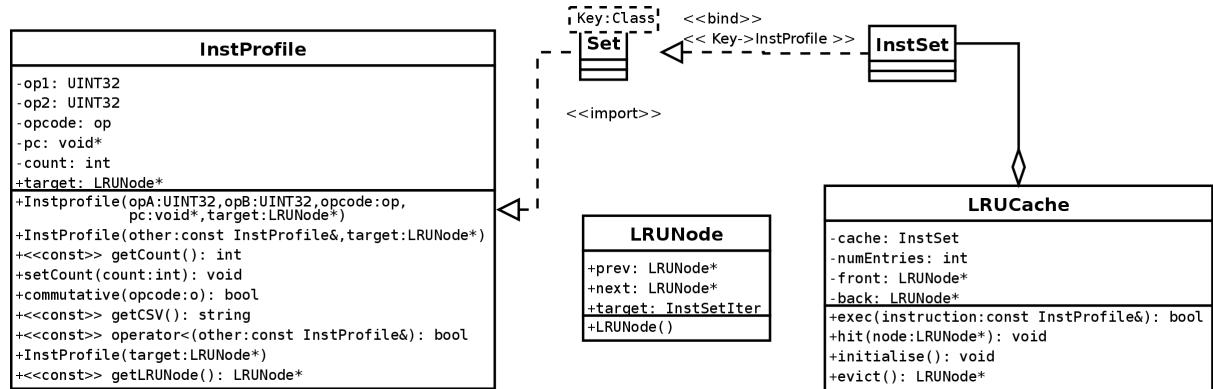

| 4.6  | Classes involved in Value Profiling Instruction Executions on the x86 architecture using Pin.                                                                                   | 29 |

| 4.7  | Classes involved in Value Profiling Instruction Executions on the x86 architecture using Pin.                                                                                   | 30 |

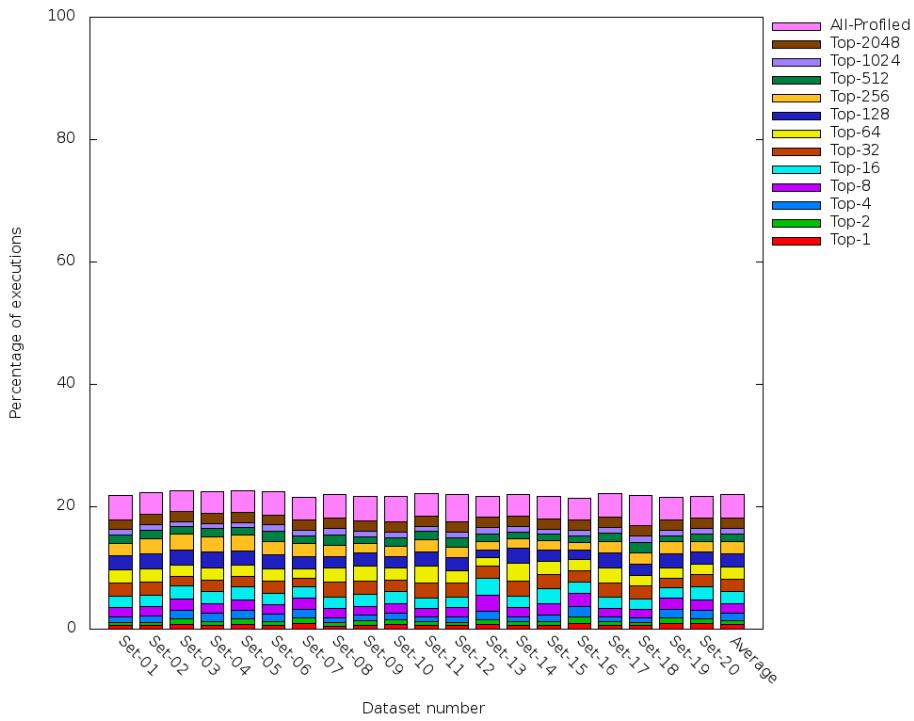

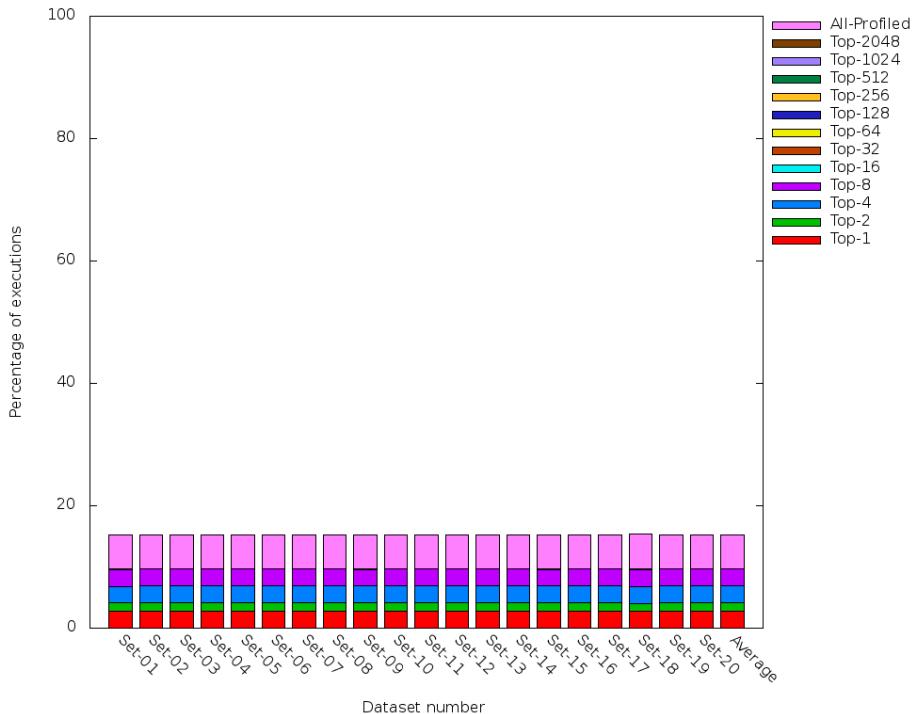

| 5.1  | Automotive-susan-c. Percentage of all profiled instructions accounted for by the top N frequently occurring instructions at global level on LLVM.                               | 54 |

| 5.2  | Automotive-susan-e. Percentage of all profiled instructions accounted for by the top N frequently occurring instructions at global level on LLVM.                               | 55 |

| 5.3  | Consumer-jpeg-c. Percentage of all profiled instructions accounted for by the top N frequently occurring instructions at global level on LLVM.                                  | 56 |

| 5.4  | Consumer-jpeg-d. Percentage of all profiled instructions accounted for by the top N frequently occurring instructions at global level on LLVM.                                  | 57 |

| 5.5  | Network-dijkstra. Percentage of all profiled instructions accounted for by the top N frequently occurring instructions at global level on LLVM.                                 | 58 |

| 5.6  | Office-stringsearch. Percentage of all profiled instructions accounted for by the top N frequently occurring instructions at global level on LLVM.                              | 59 |

| 5.7  | Security rijndael-d. Percentage of all profiled instructions accounted for by the top N frequently occurring instructions at global level on LLVM.                              | 60 |

| 5.8  | Security-sha. Percentage of all profiled instructions accounted for by the top N frequently occurring instructions at global level on LLVM.                                     | 61 |

| 5.9  | Telecom-adpcm-c. Percentage of all profiled instructions accounted for by the top N frequently occurring instructions at global level on LLVM.                                  | 62 |

| 5.10 | Telecom-adpcm-d. Percentage of all profiled instructions accounted for by the top N frequently occurring instructions at global level on LLVM.                                  | 63 |

| 5.11 | Telecom-crc32. Percentage of all profiled instructions accounted for by the top N frequently occurring instructions at global level on LLVM.                                    | 64 |

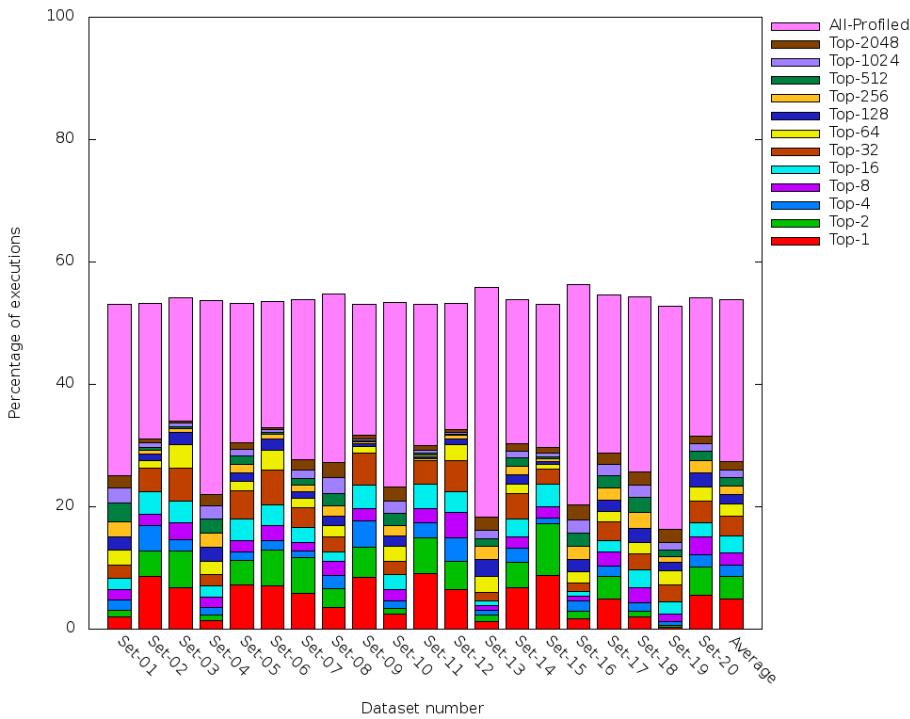

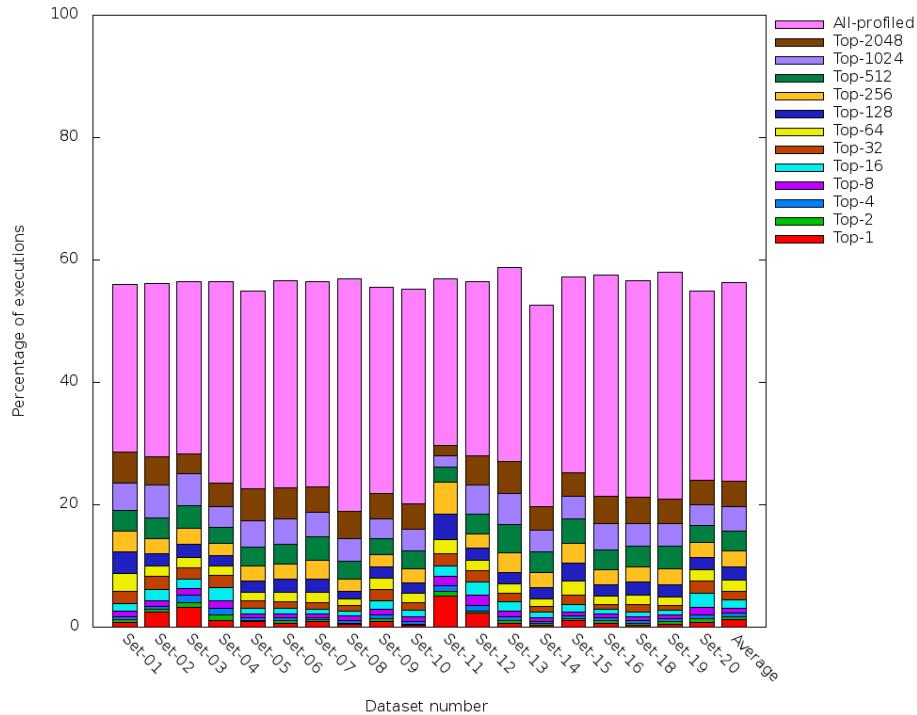

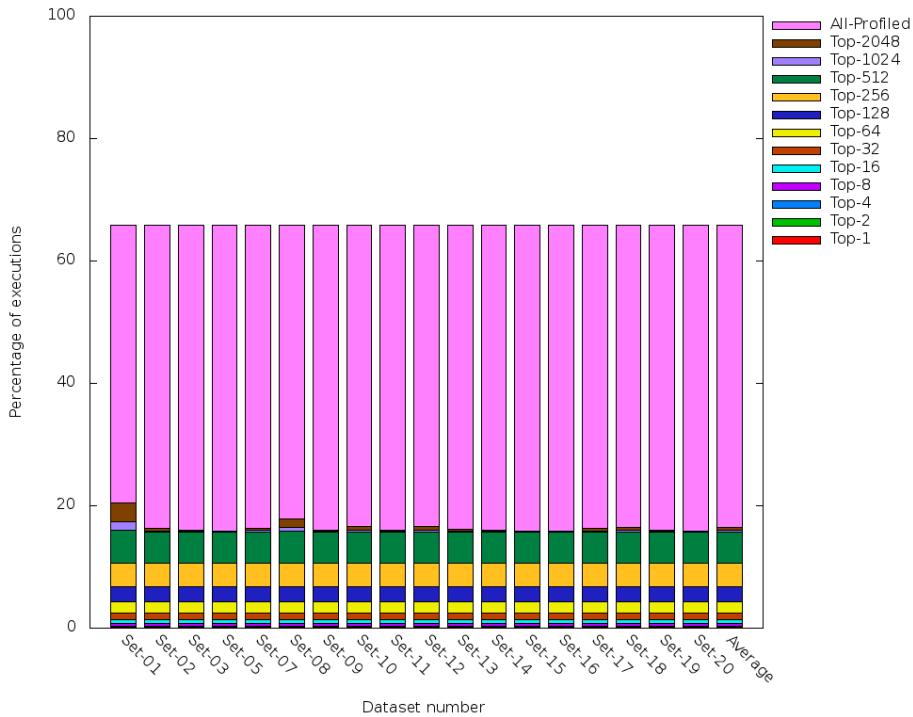

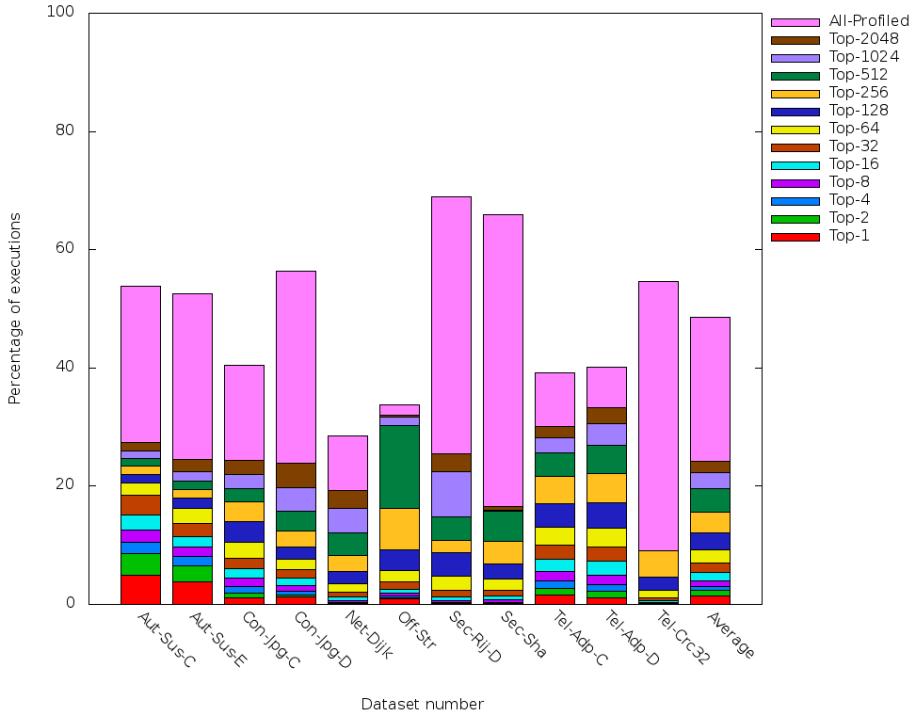

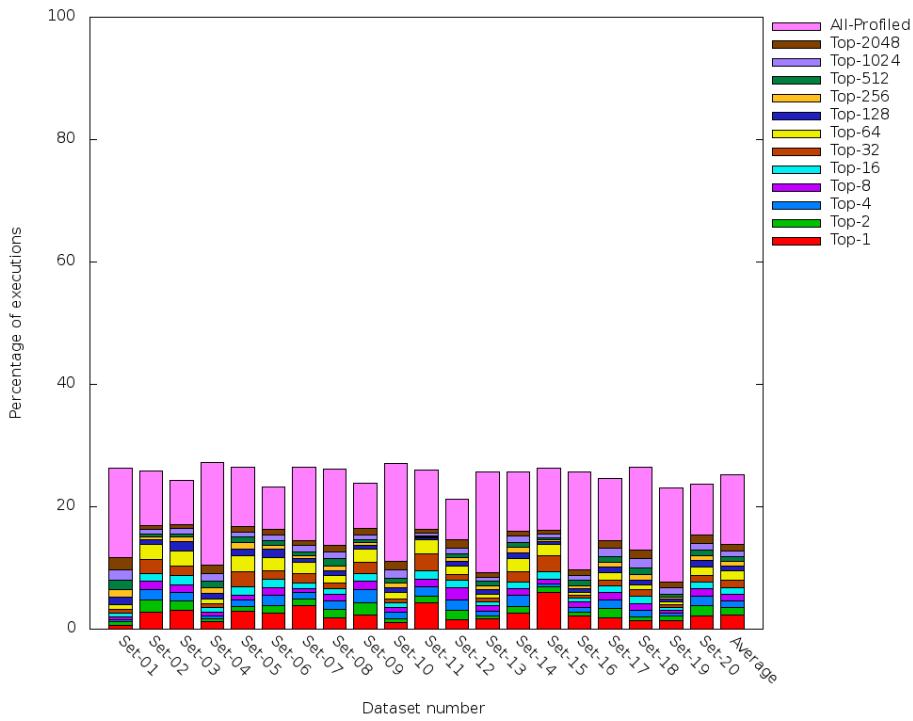

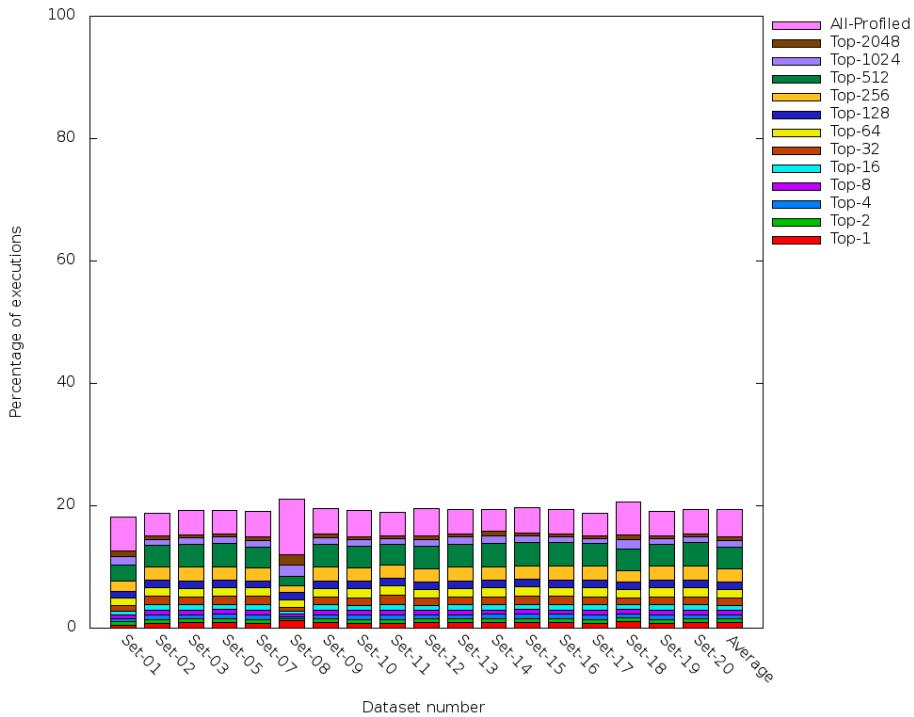

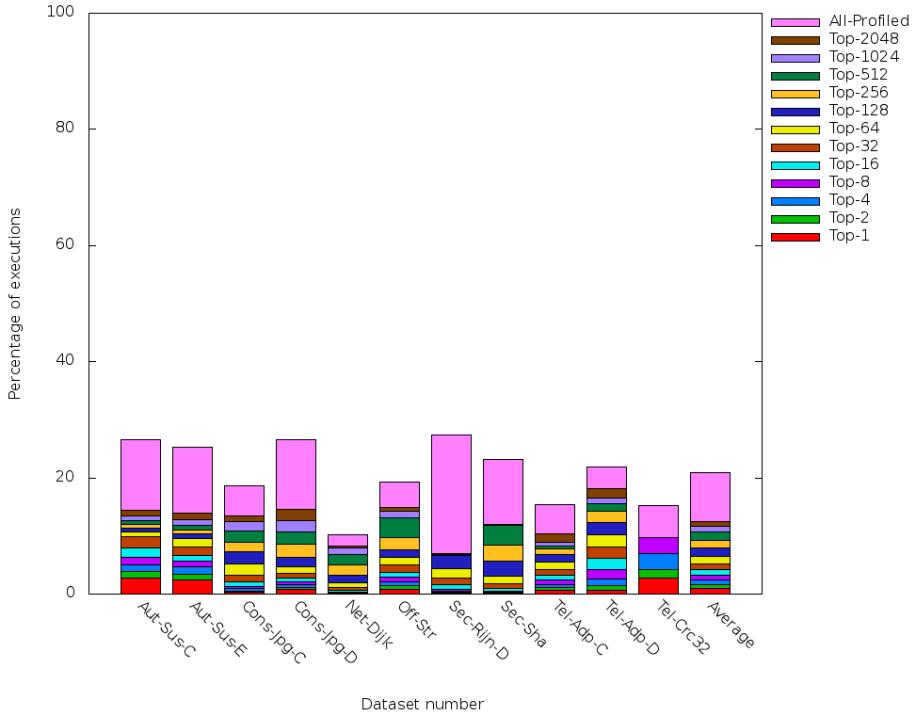

| 5.12 | Comparison of the percentage of all instruction executions accounted for by the top N frequently occurring instructions across all benchmarks at global level on LLVM.          | 65 |

| 5.13 | Comparison of the percentage of all profiled instruction executions accounted for by the top N frequently occurring instructions across all benchmarks at global level on LLVM. | 66 |

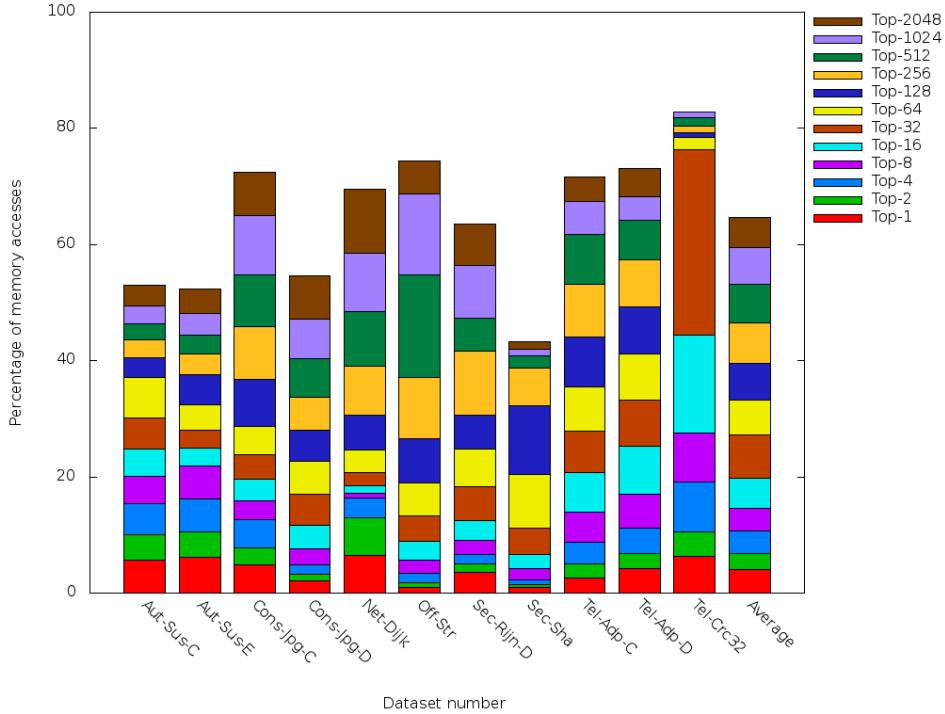

| 5.14 | Automotive-susan-c. Percentage of all memory accesses accounted for by the top N most frequently transferred values at global level on LLVM.                                    | 67 |

| 5.15 | Automotive-susan-e. Percentage of all memory accesses accounted for by the top N most frequently transferred values at global level on LLVM.                                    | 67 |

| 5.16 | Consumer-jpeg-c. Percentage of all memory accesses accounted for by the top N most frequently transferred values at global level on LLVM.                                       | 68 |

|      |                                                                                                                                                                                          |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.17 | Consumer-jpeg-d. Percentage of all memory accesses accounted for by the top N most frequently transferred values at global level on LLVM. . . . .                                        | 69 |

| 5.18 | Network-dijkstra. Percentage of all memory accesses accounted for by the top N most frequently transferred values at global level on LLVM. . . . .                                       | 70 |

| 5.19 | Office-stringsearch. Percentage of all memory accesses accounted for by the top N most frequently transferred values at global level on LLVM. . . . .                                    | 70 |

| 5.20 | Security rijndael-d. Percentage of all memory accesses accounted for by the top N most frequently transferred values at global level on LLVM. . . . .                                    | 71 |

| 5.21 | Security-sha. Percentage of all memory accesses accounted for by the top N most frequently transferred values at global level on LLVM. . . . .                                           | 72 |

| 5.22 | Telecom-adpcm-c. Percentage of all memory accesses accounted for by the top N most frequently transferred values at global level on LLVM. . . . .                                        | 73 |

| 5.23 | Telecom-adpcm-d. Percentage of all memory accesses accounted for by the top N most frequently transferred values at global level on LLVM. . . . .                                        | 74 |

| 5.24 | Telecom-crc32. Percentage of all memory accesses accounted for by the top N most frequently transferred values at global level on LLVM. . . . .                                          | 74 |

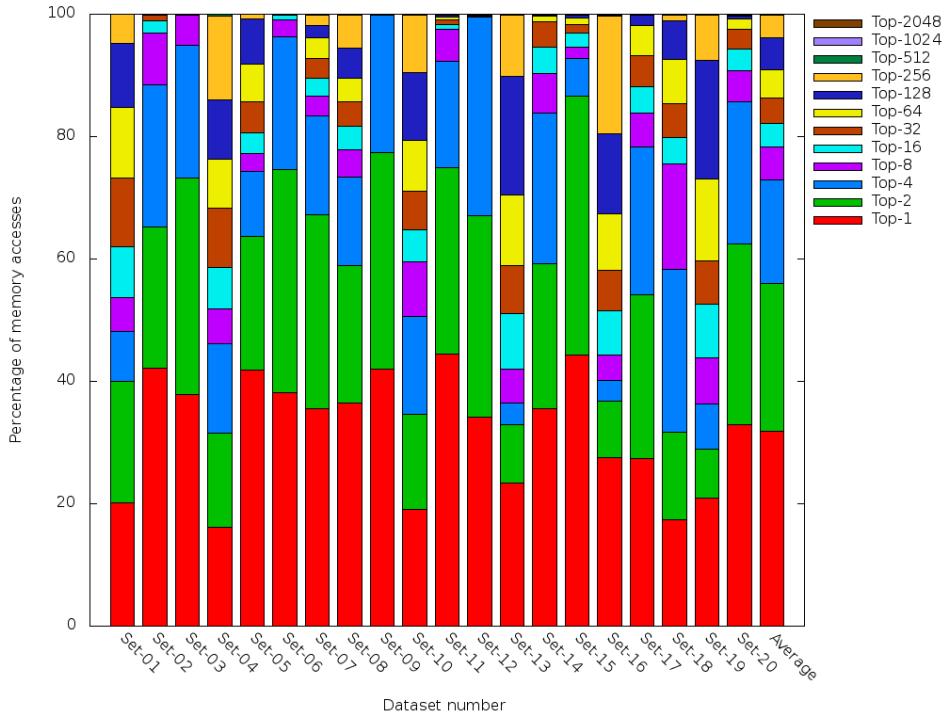

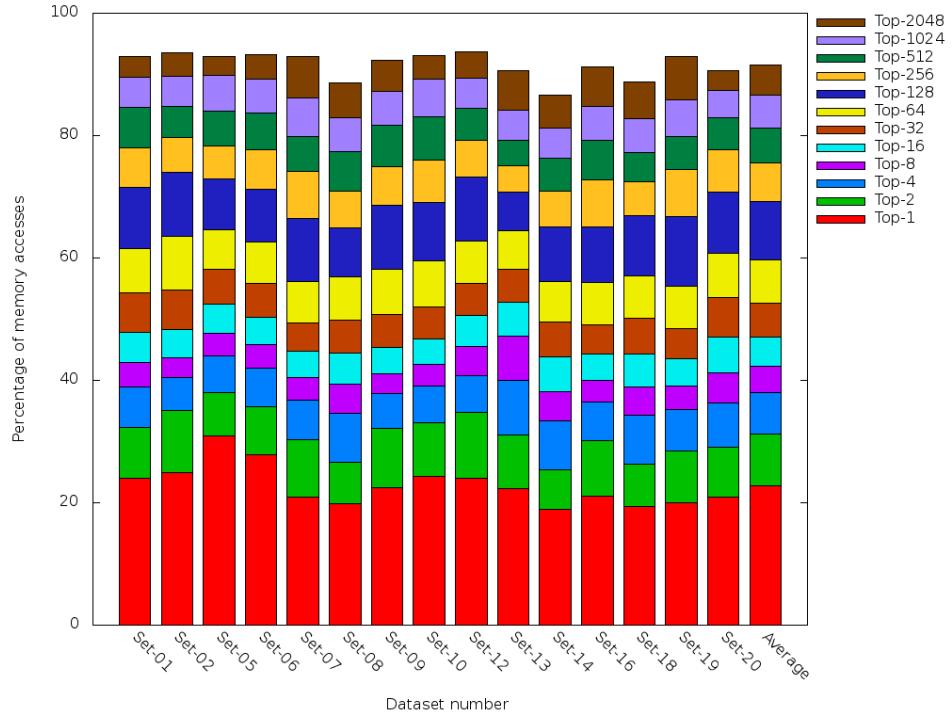

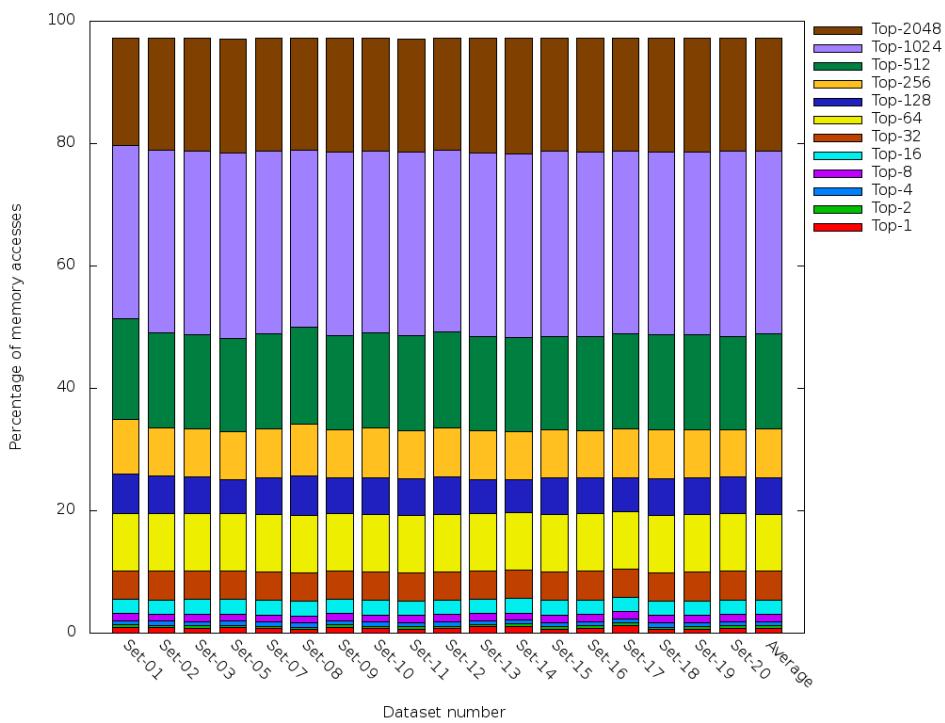

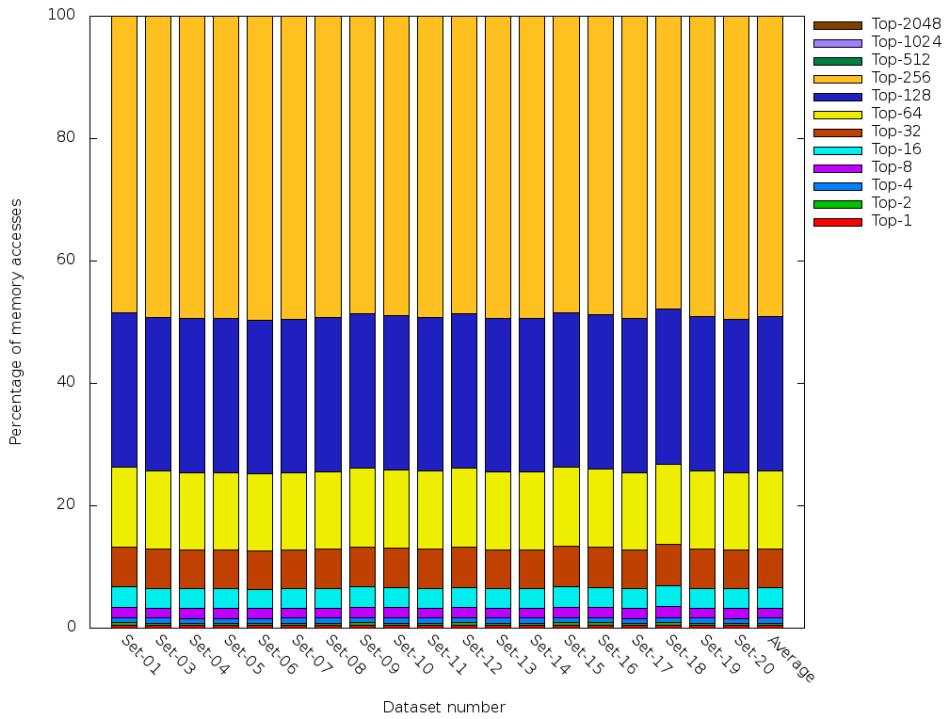

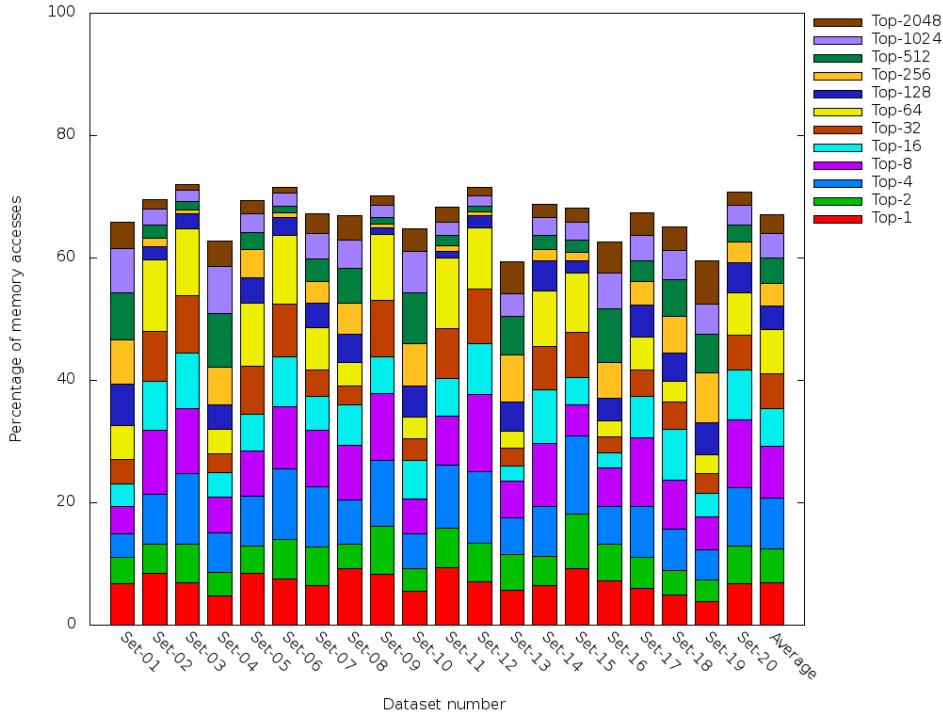

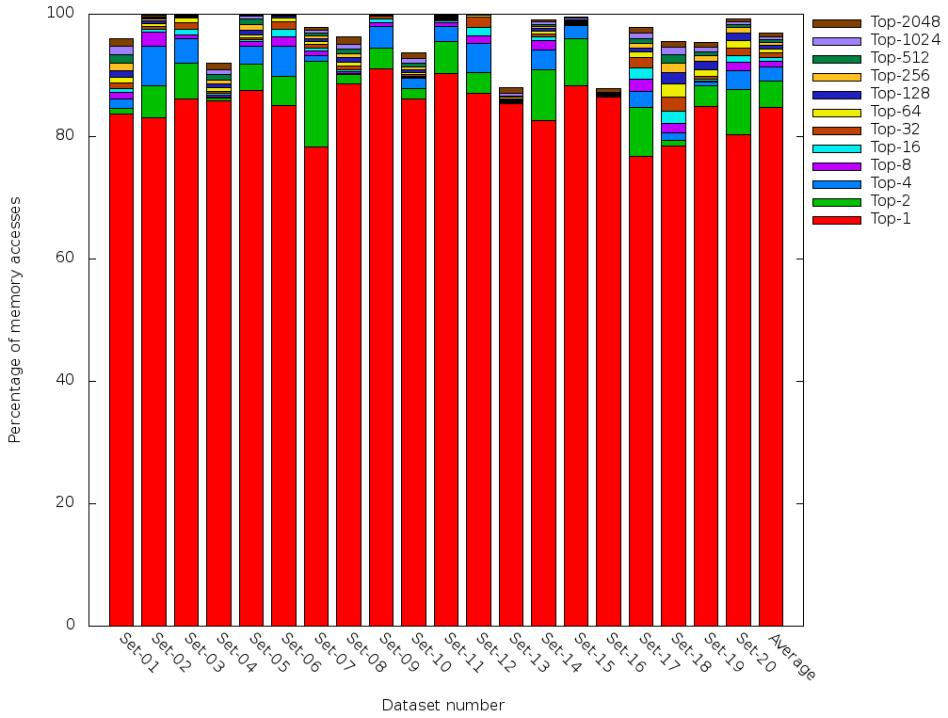

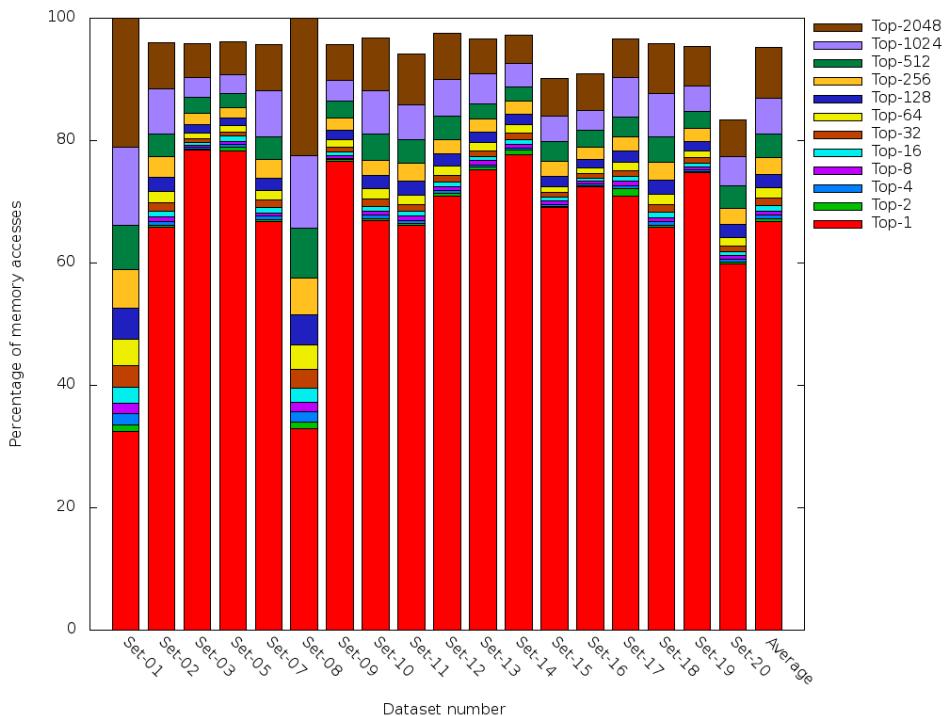

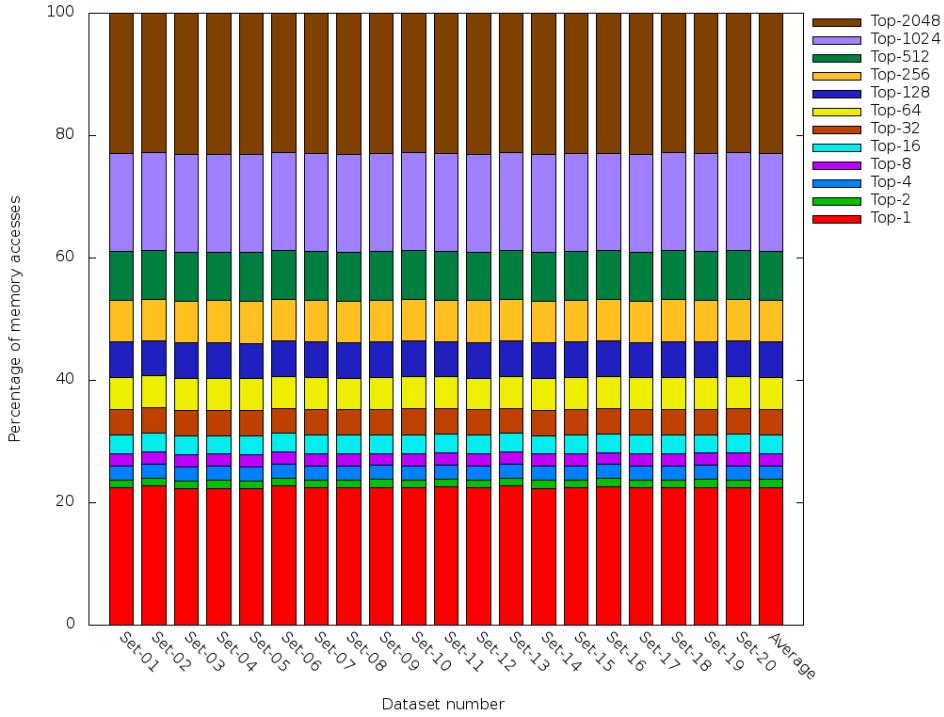

| 5.25 | Comparison of the percentage of all memory accesses accounted for by the top N most frequently transferred values across all benchmarks at global level on LLVM. . . . .                 | 76 |

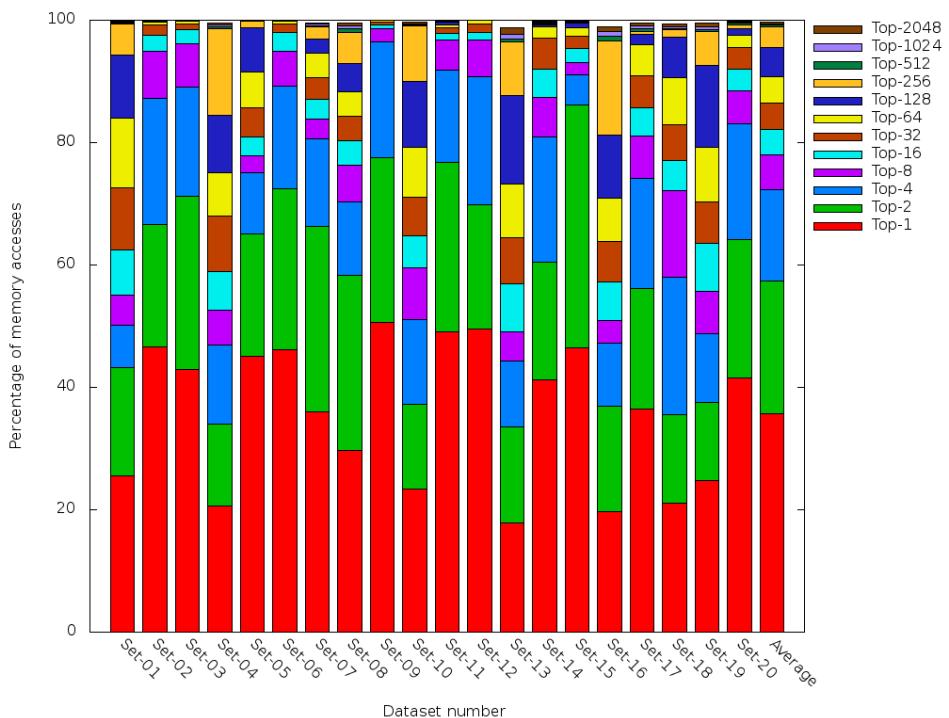

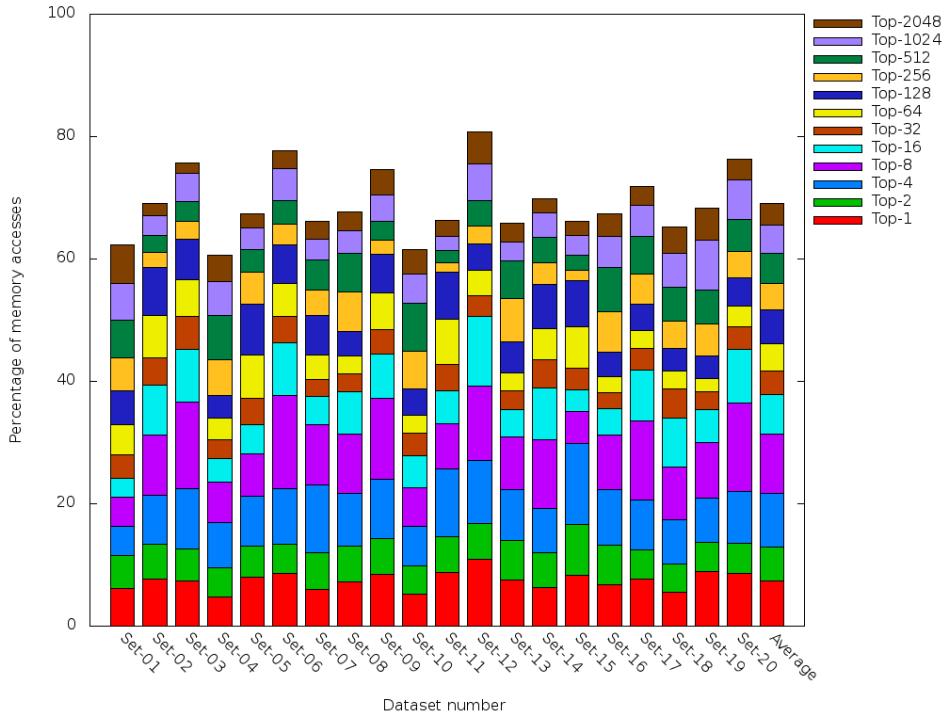

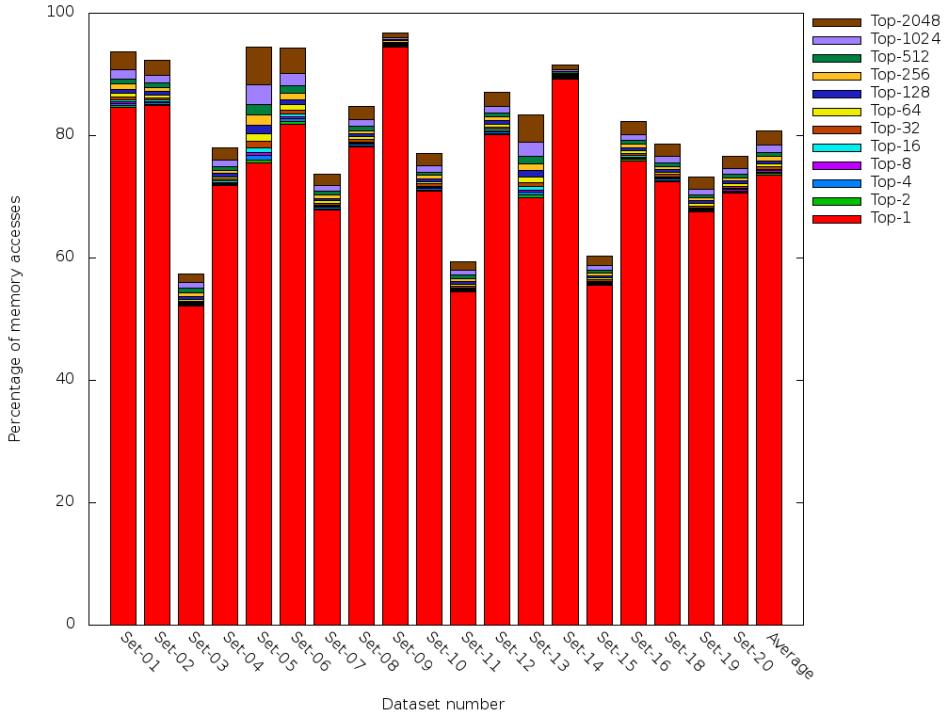

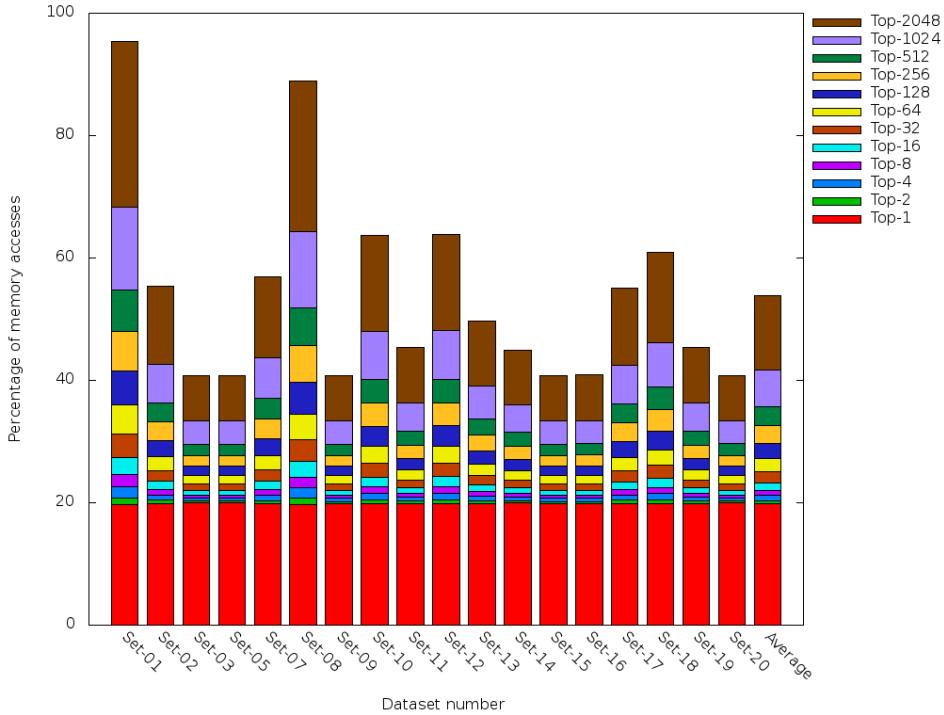

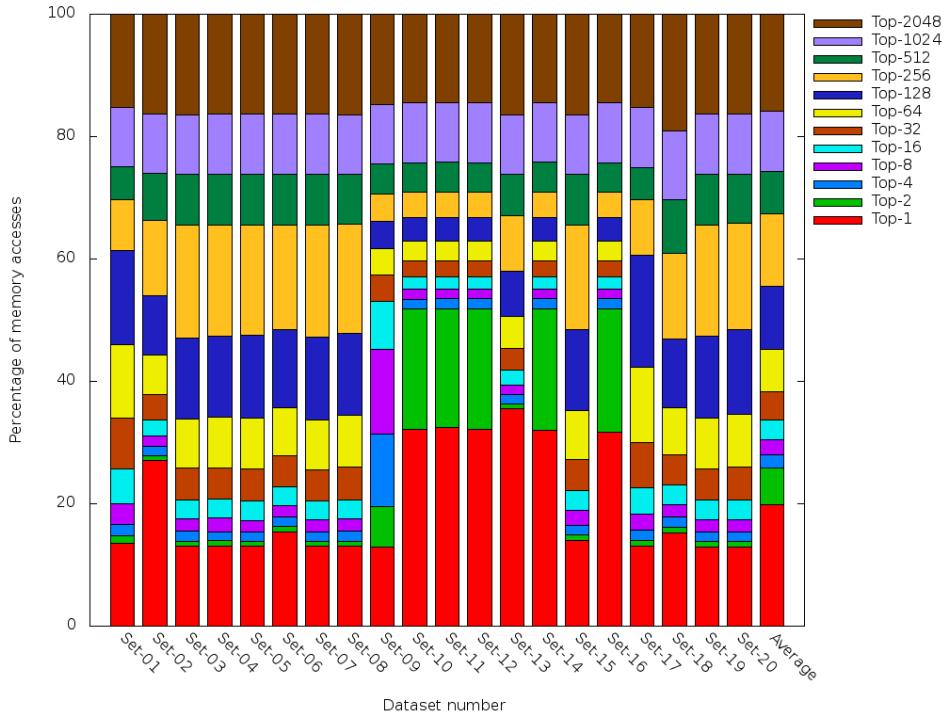

| 5.26 | Comparison of the percentage of all memory accesses accounted for by the top N most frequently transferred values across all benchmarks at local level on LLVM. . . . .                  | 76 |

| 5.27 | Automotive-susan-c. Percentage of all profiled instructions accounted for by the top N frequently occurring instructions at global level profiled using Pin. . . . .                     | 77 |

| 5.28 | Automotive-susan-e. Percentage of all profiled instructions accounted for by the top N frequently occurring instructions at global level profiled using Pin. . . . .                     | 78 |

| 5.29 | Consumer-jpeg-c. Percentage of all profiled instructions accounted for by the top N frequently occurring instructions at global level profiled using Pin. . . . .                        | 78 |

| 5.30 | Consumer-jpeg-d. Percentage of all profiled instructions accounted for by the top N frequently occurring instructions at global level profiled using Pin. . . . .                        | 79 |

| 5.31 | Network-dijkstra. Percentage of all profiled instructions accounted for by the top N frequently occurring instructions at global level profiled using Pin. . . . .                       | 80 |

| 5.32 | Office-stringsearch. Percentage of all profiled instructions accounted for by the top N frequently occurring instructions at global level profiled using Pin. . . . .                    | 80 |

| 5.33 | Security rijndael-d. Percentage of all profiled instructions accounted for by the top N frequently occurring instructions at global level profiled using Pin. . . . .                    | 81 |

| 5.34 | Security-sha. Percentage of all profiled instructions accounted for by the top N frequently occurring instructions at global level profiled using Pin. . . . .                           | 82 |

| 5.35 | Telecom-adpcm-c. Percentage of all profiled instructions accounted for by the top N frequently occurring instructions at global level profiled using Pin. . . . .                        | 82 |

| 5.36 | Telecom-adpcm-d. Percentage of all profiled instructions accounted for by the top N frequently occurring instructions at global level profiled using Pin. . . . .                        | 83 |

| 5.37 | Telecom-crc32. Percentage of all profiled instructions accounted for by the top N frequently occurring instructions at global level profiled using Pin. . . . .                          | 83 |

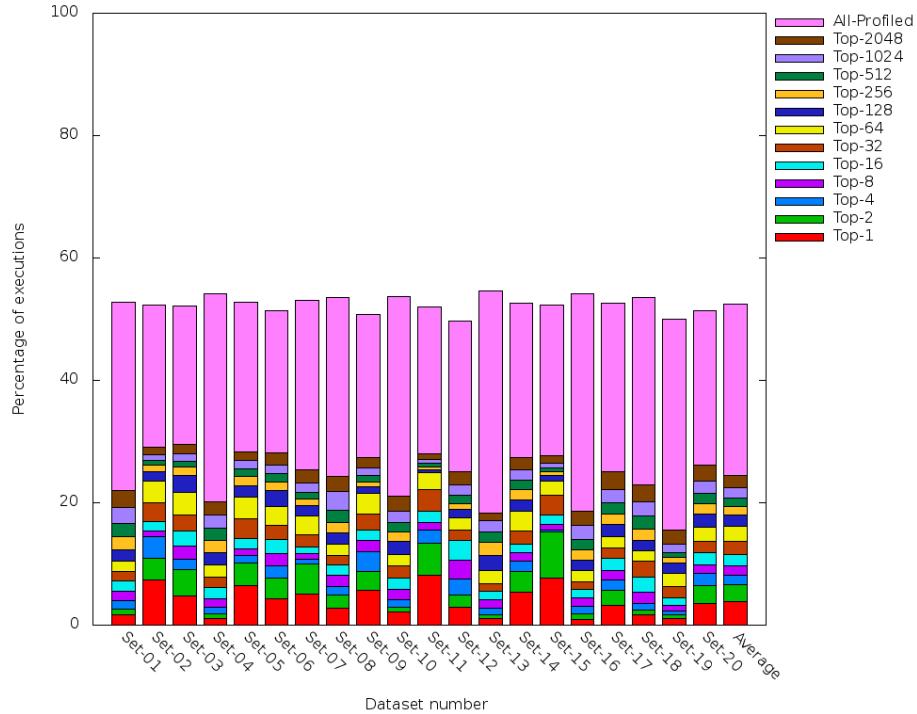

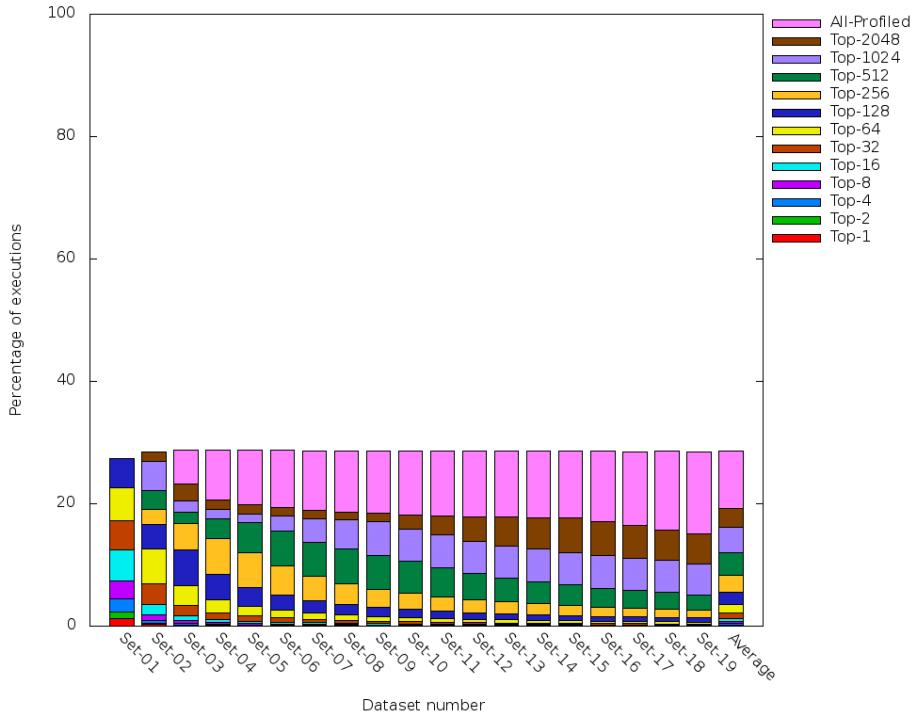

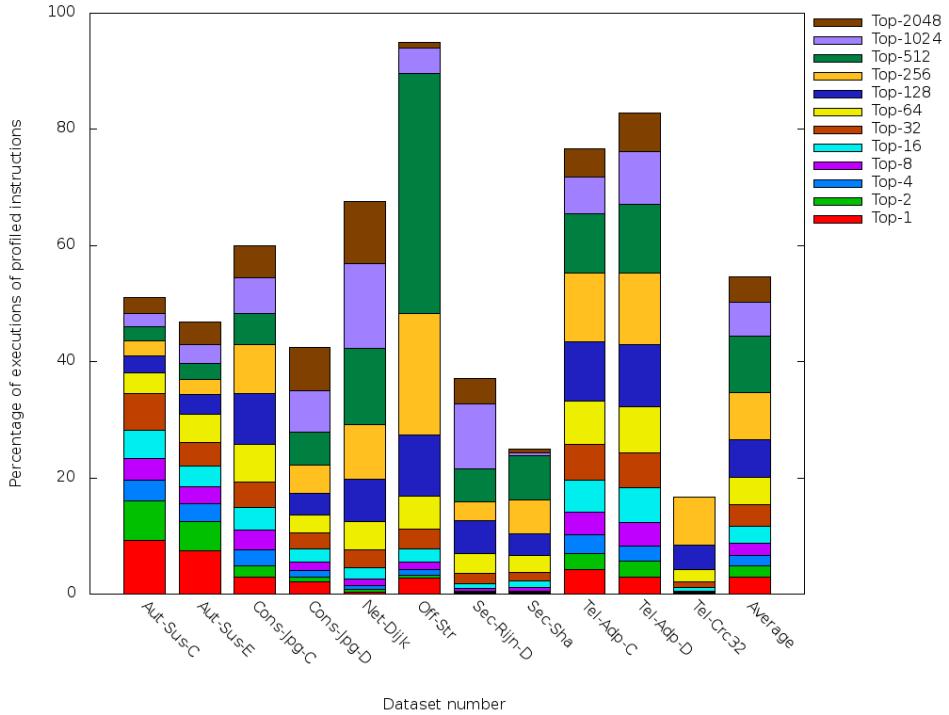

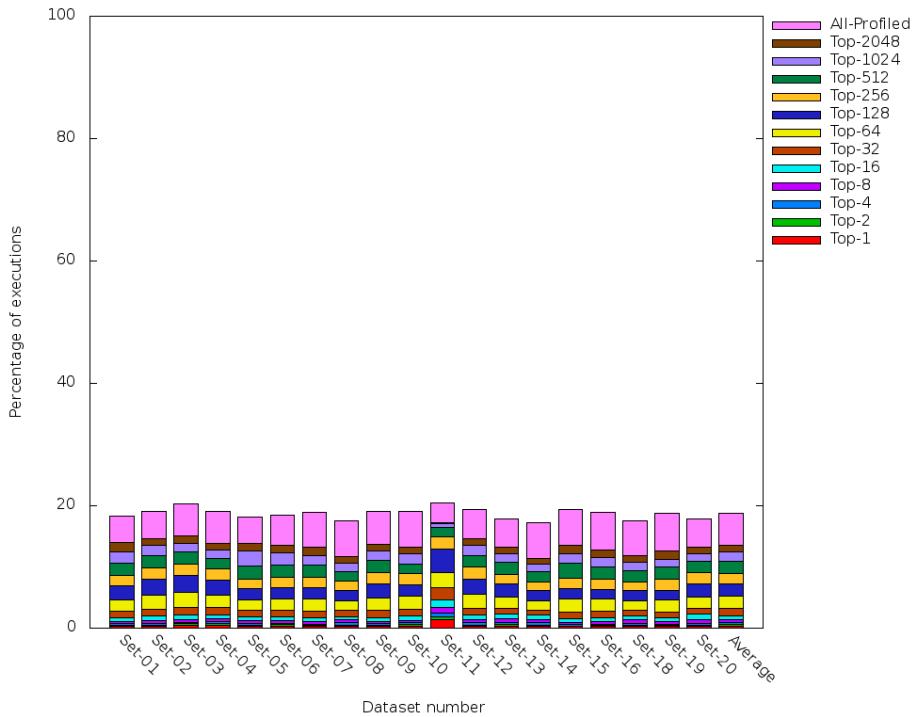

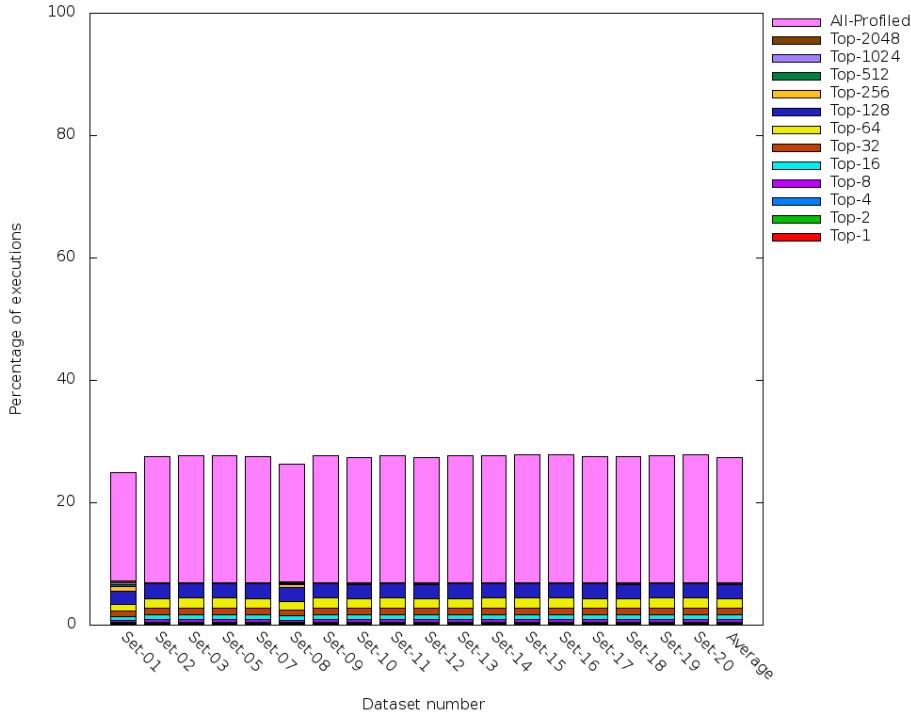

| 5.38 | Comparison across all benchmarks of the percentage of all instructions accounted for by the top N frequently occurring instructions at global level profiled using Pin. . . . .          | 84 |

| 5.39 | Comparison across all benchmarks of the percentage of all profiled instructions accounted for by the top N frequently occurring instructions at global level profiled using Pin. . . . . | 85 |

| 5.40 | Automotive-susan-c. Percentage of all memory accesses accounted for by the top N most frequently transferred values at global level using Pin. . . . .                                   | 86 |

| 5.41 | Automotive-susan-e. Percentage of all memory accesses accounted for by the top N most frequently transferred values at global level using Pin. . . . .                                   | 87 |

| 5.42 | Consumer-jpeg-c. Percentage of all memory accesses accounted for by the top N most frequently transferred values at global level using Pin. . . . .                                      | 87 |

| 5.43 | Consumer-jpeg-d. Percentage of all memory accesses accounted for by the top N most frequently transferred values at global level using Pin. . . . .                                      | 88 |

| 5.44 | Network-dijkstra. Percentage of all memory accesses accounted for by the top N most frequently transferred values at global level using Pin. . . . .                                     | 89 |

|      |                                                                                                                                                                            |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.45 | Office-stringsearch. Percentage of all memory accesses accounted for by the top N most frequently transferred values at global level using Pin. . . . .                    | 89  |

| 5.46 | Security-rijndael-d. Percentage of all memory accesses accounted for by the top N most frequently transferred values at global level using Pin. . . . .                    | 90  |

| 5.47 | Security-sha. Percentage of all memory accesses accounted for by the top N most frequently transferred values at global level using Pin. . . . .                           | 91  |

| 5.48 | Telecom-adpcm-c. Percentage of all memory accesses accounted for by the top N most frequently transferred values at global level using Pin. . . . .                        | 91  |

| 5.49 | Telecom-adpcm-d. Percentage of all memory accesses accounted for by the top N most frequently transferred values at global level using Pin. . . . .                        | 92  |

| 5.50 | Telecom-crc32. Percentage of all memory accesses accounted for by the top N most frequently transferred values at global level using Pin. . . . .                          | 93  |

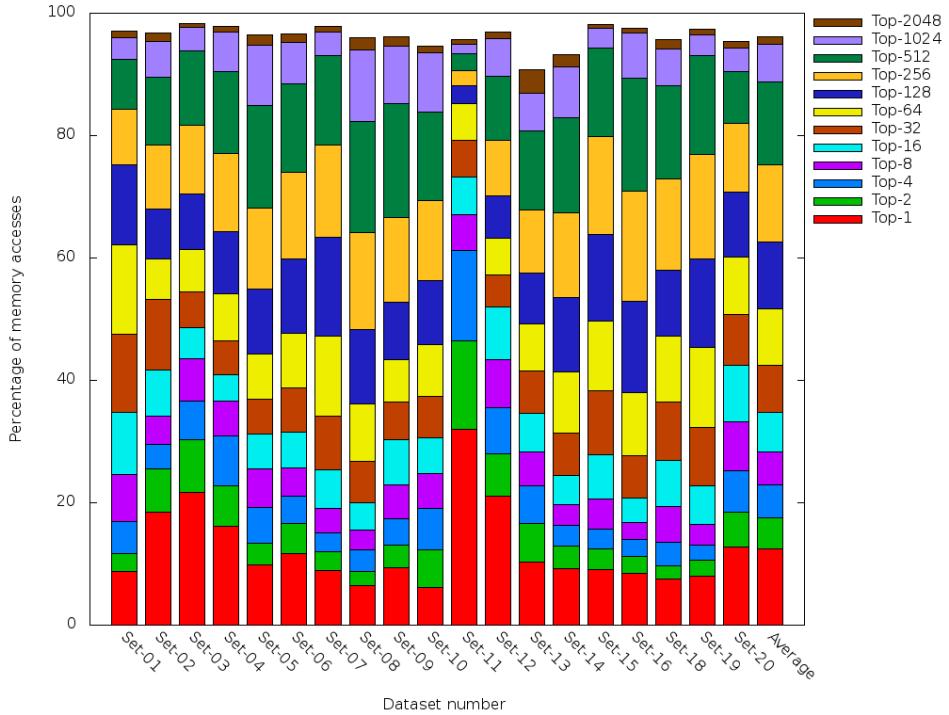

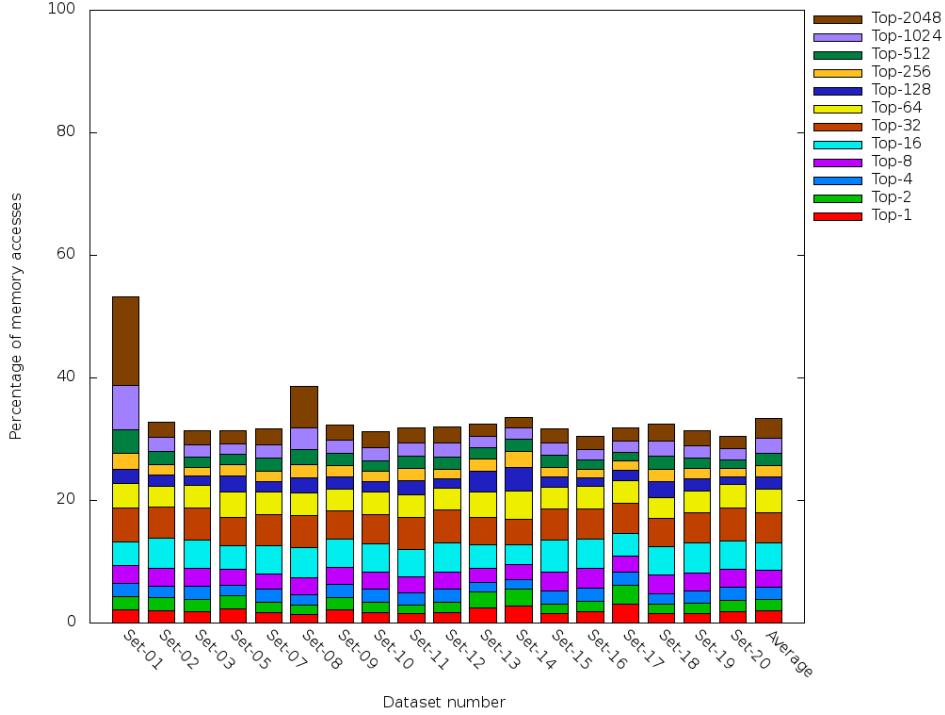

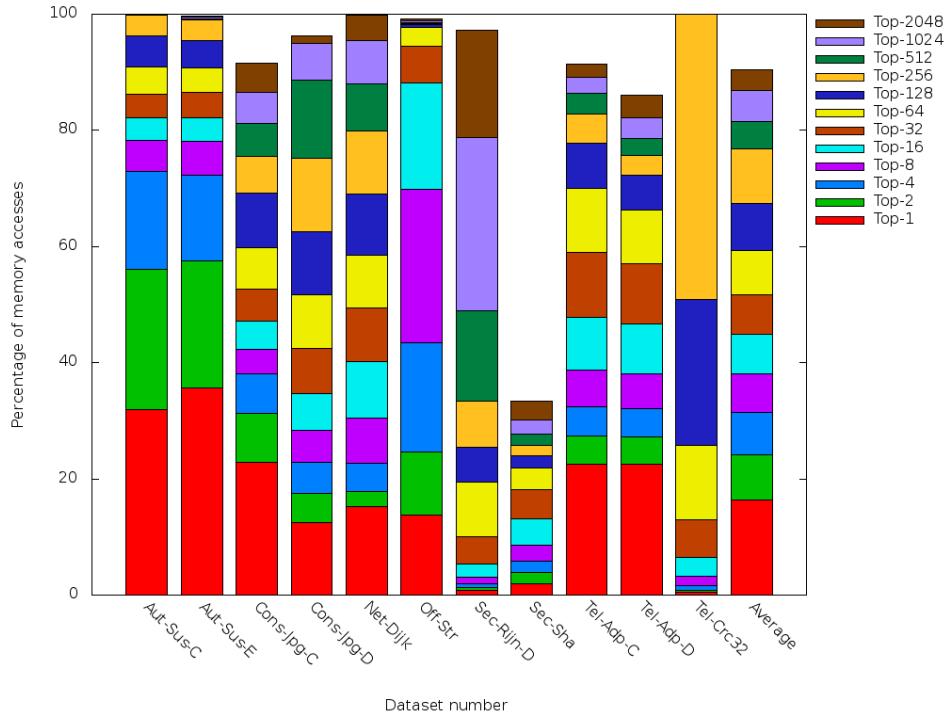

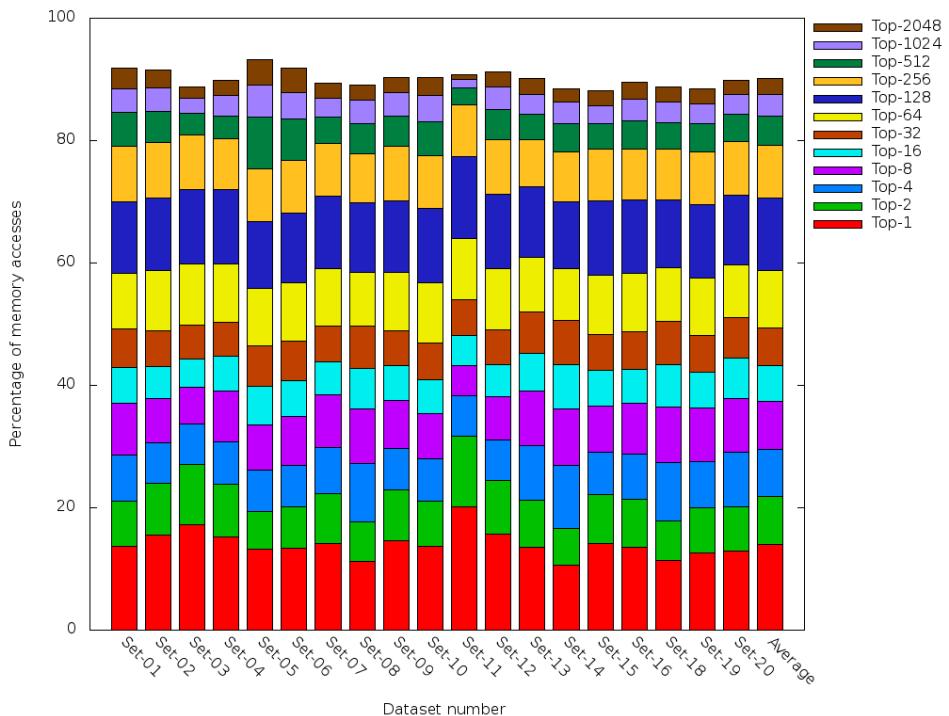

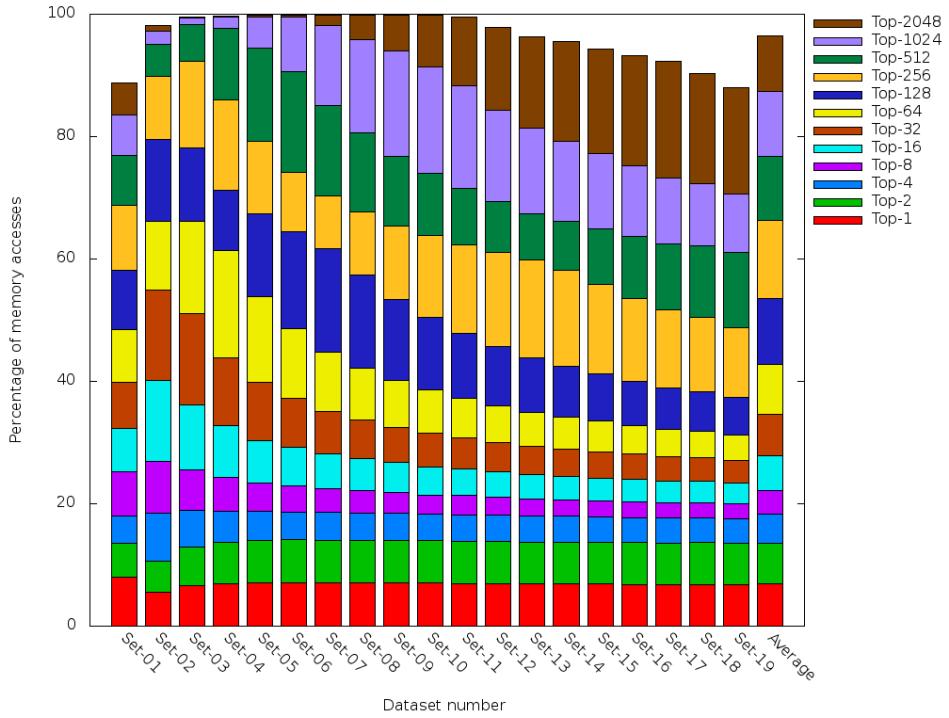

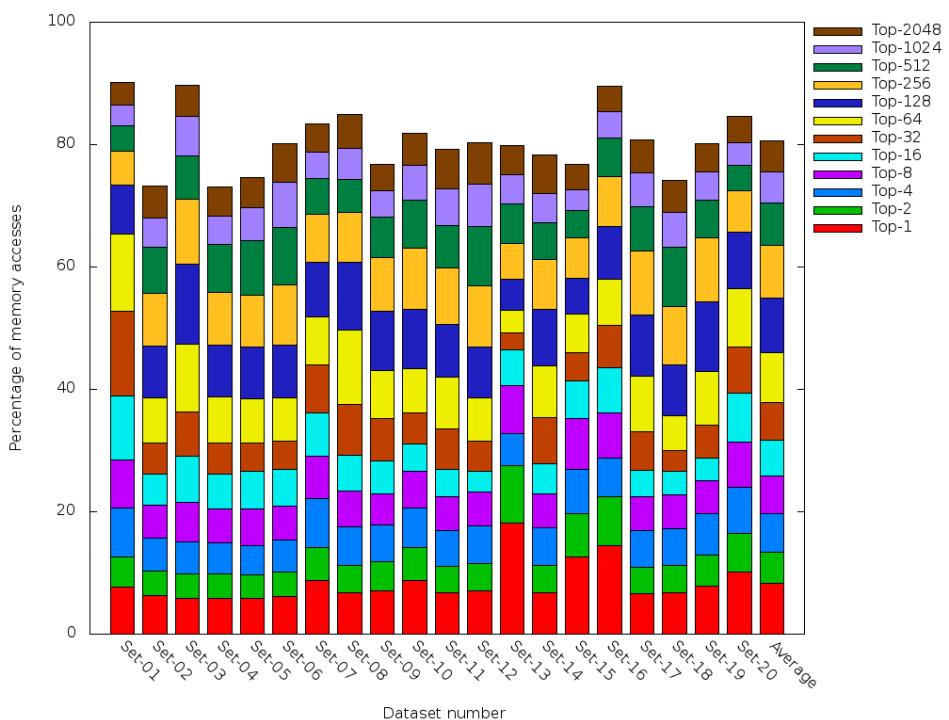

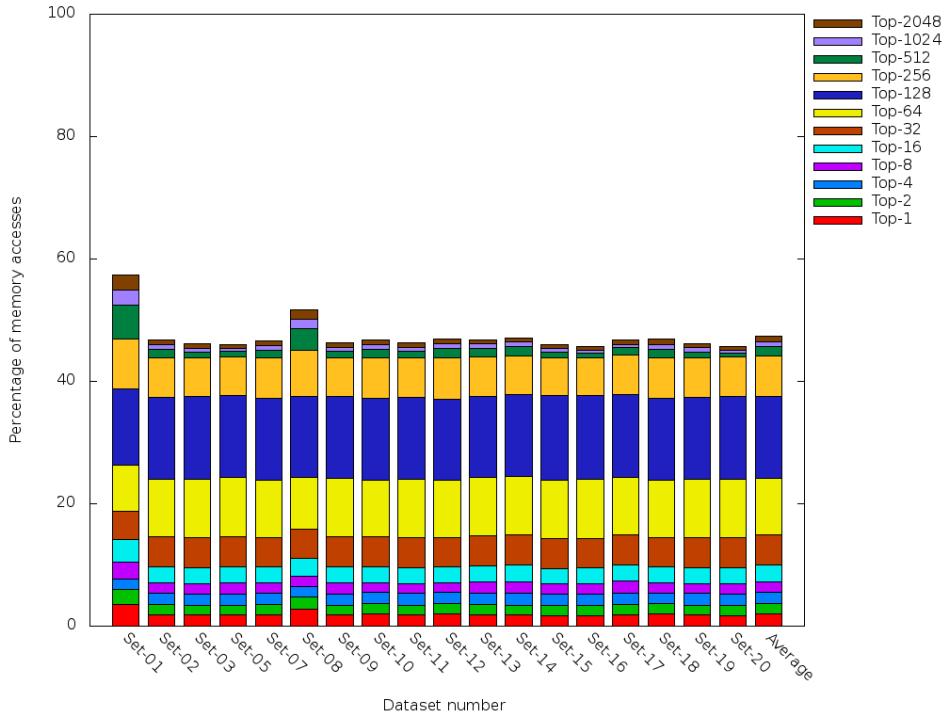

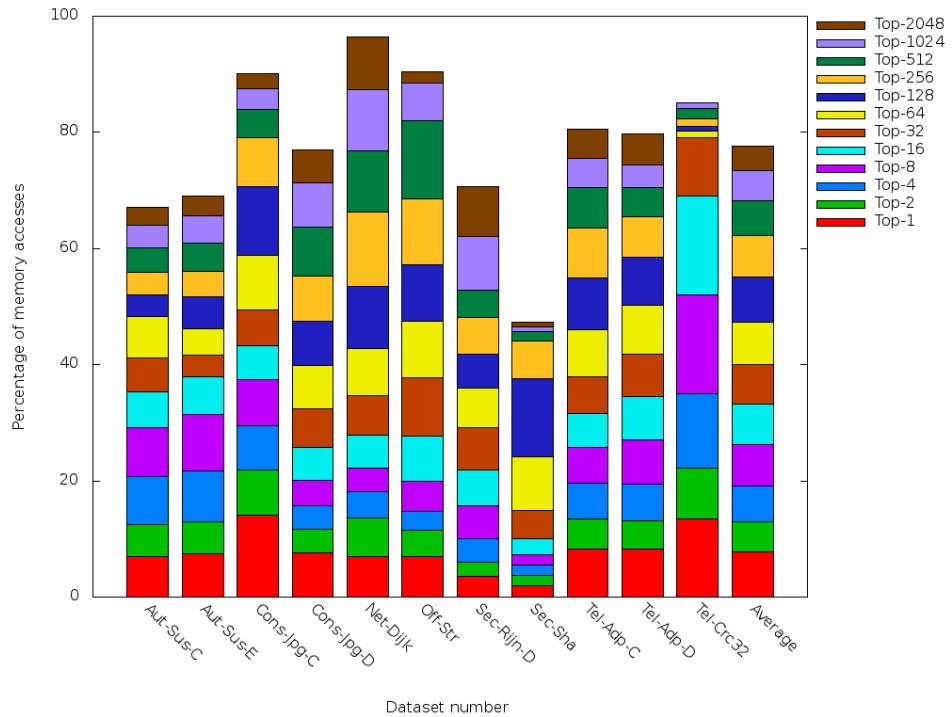

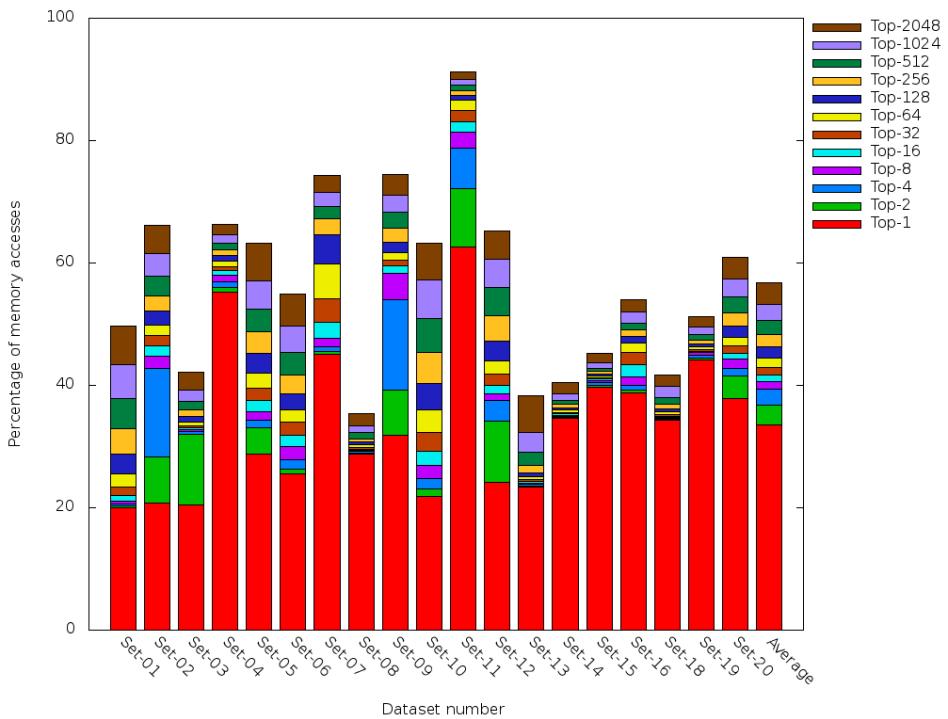

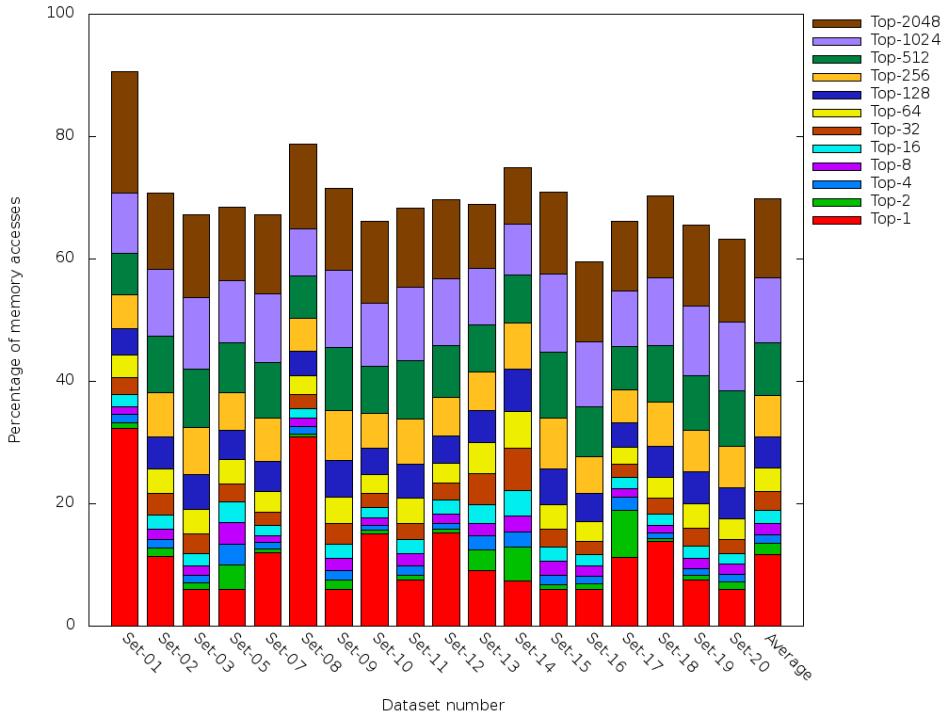

| 5.51 | Comparison of the percentage of all memory accesses accounted for by the top N most frequently transferred values across all benchmarks at global level using Pin. . . . . | 93  |

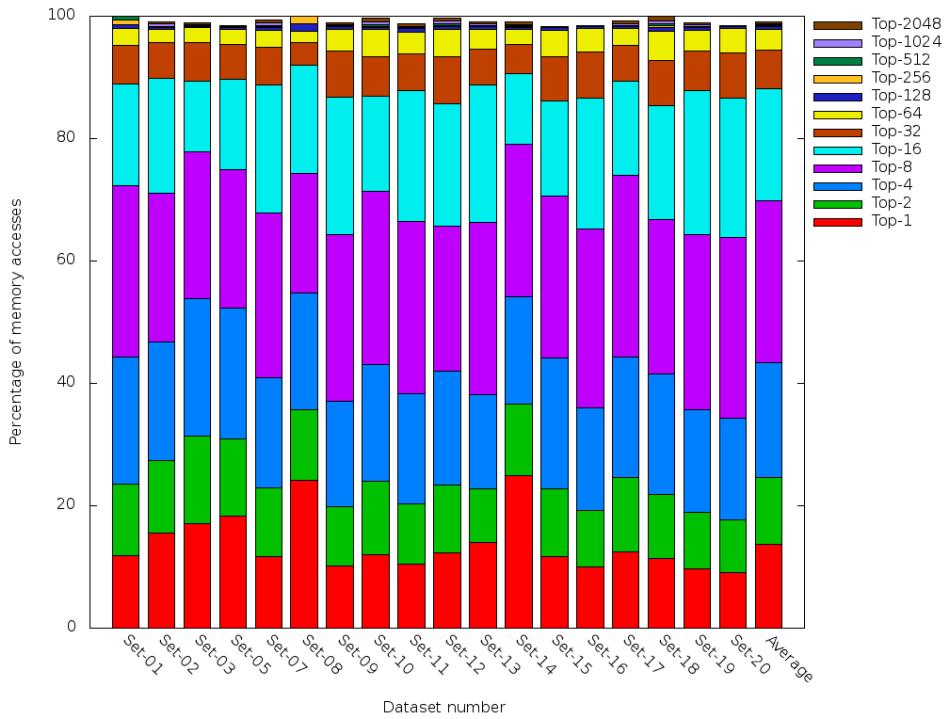

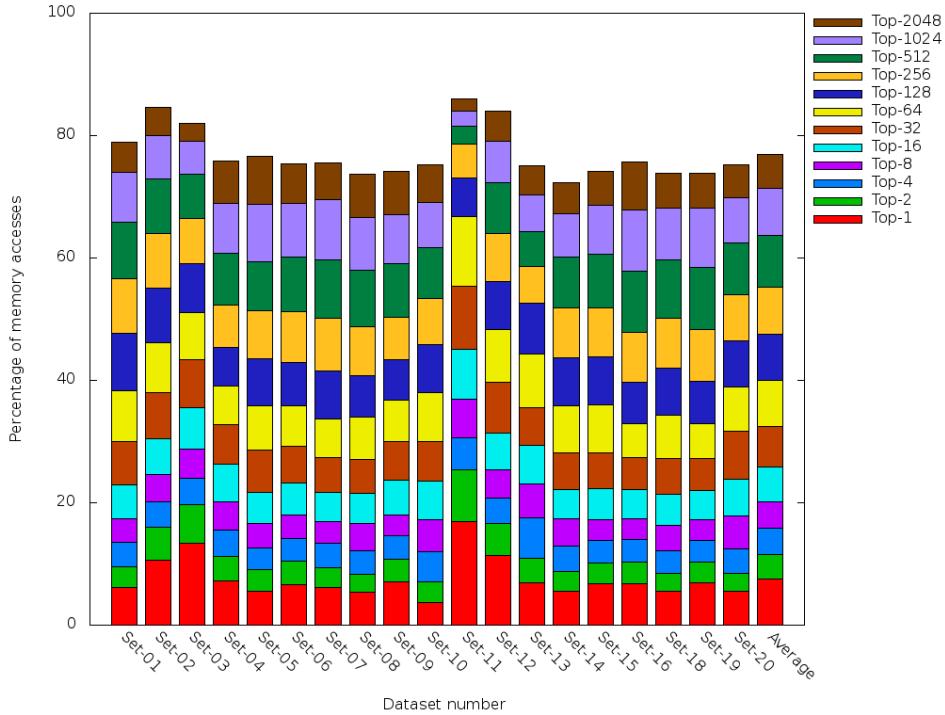

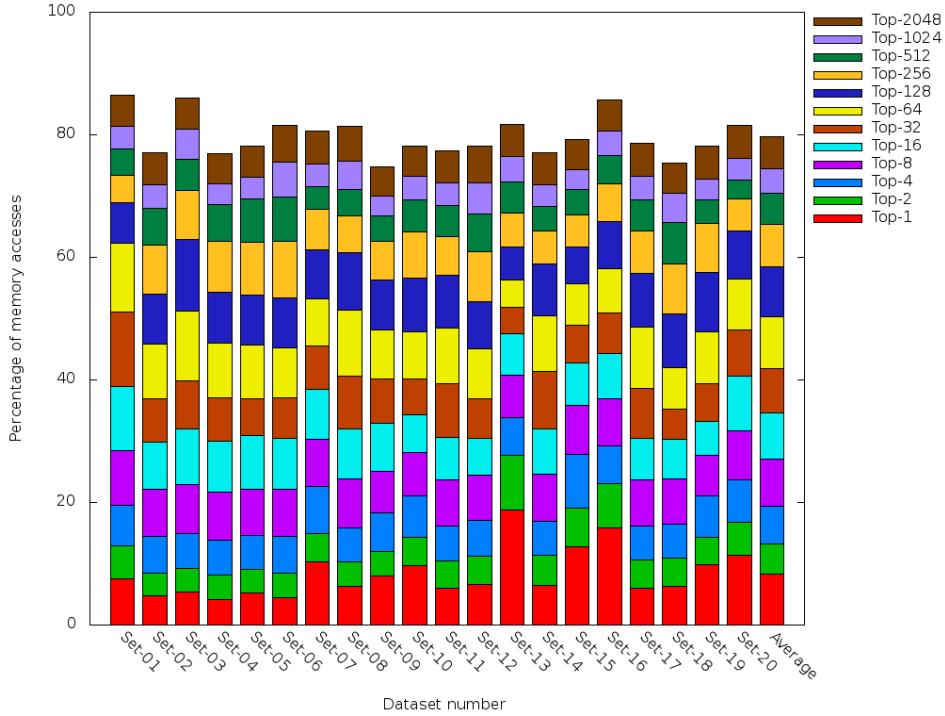

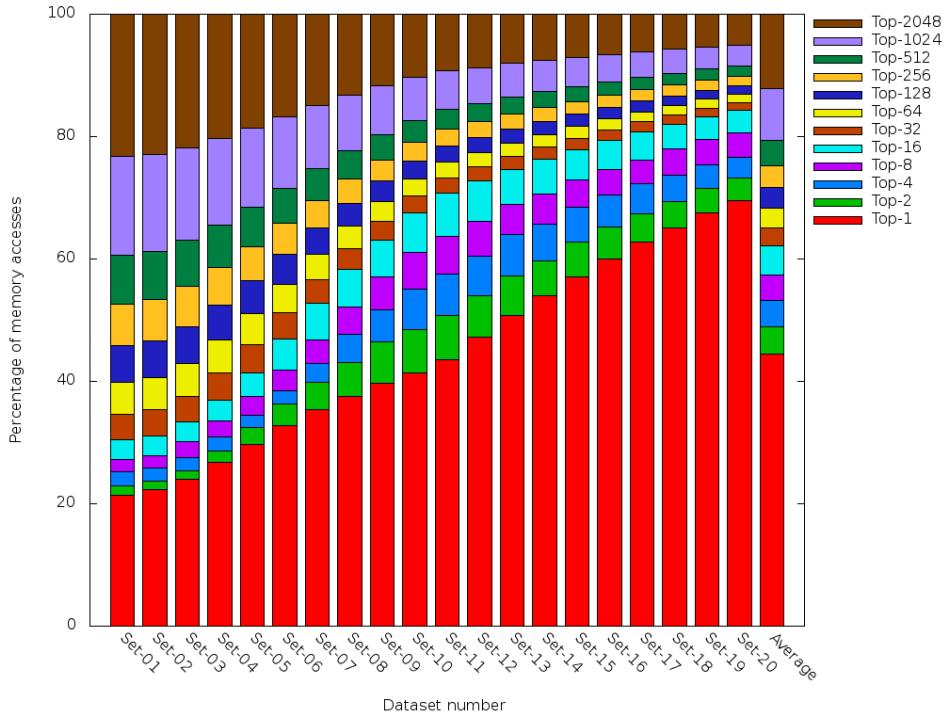

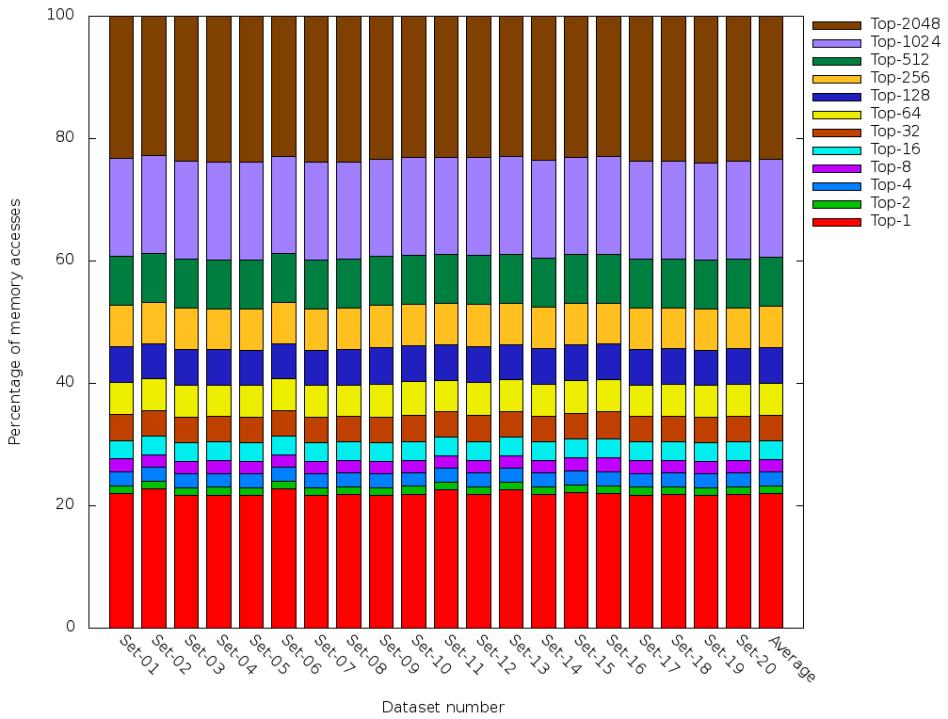

| 5.52 | Comparison of the percentage of all memory accesses accounted for by the top N most frequently transferred values across all benchmarks at local level using Pin. . . . .  | 94  |

| 6.1  | Classes involved in the implementation of the Value Reuse Cache. . . . .                                                                                                   | 97  |

| 6.2  | Automotive-susan-c. Cache hit rate for specified sizes of Global-Level Value Reuse Cache, and total percentage of cacheable instructions. . . . .                          | 103 |

| 6.3  | Automotive-susan-e. Cache hit rate for specified sizes of Global-Level Value Reuse Cache, and total percentage of cacheable instructions. . . . .                          | 103 |

| 6.4  | Consumer-Jpeg-C. Cache hit rate for specified sizes of Global-Level Value Reuse Cache, and total percentage of cacheable instructions. . . . .                             | 104 |

| 6.5  | Consumer-Jpeg-D. Cache hit rate for specified sizes of Global-Level Value Reuse Cache, and total percentage of cacheable instructions. . . . .                             | 105 |

| 6.6  | Network-Dijkstra. Cache hit rate for specified sizes of Global-Level Value Reuse Cache, and total percentage of cacheable instructions. . . . .                            | 106 |

| 6.7  | Office-Stringsearch. Cache hit rate for specified sizes of Global-Level Value Reuse Cache, and total percentage of cacheable instructions. . . . .                         | 106 |

| 6.8  | Security-Rijndael-D. Cache hit rate for specified sizes of Global-Level Value Reuse Cache, and total percentage of cacheable instructions. . . . .                         | 107 |

| 6.9  | Security-Sha. Cache hit rate for specified sizes of Global-Level Value Reuse Cache, and total percentage of cacheable instructions. . . . .                                | 108 |

| 6.10 | Telecom-Adpcm-C. Cache hit rate for specified sizes of Global-Level Value Reuse Cache, and total percentage of cacheable instructions. . . . .                             | 109 |

| 6.11 | Telecom-Adpcm-D. Cache hit rate for specified sizes of Global-Level Value Reuse Cache, and total percentage of cacheable instructions. . . . .                             | 110 |

| 6.12 | Telecom-Crc32. Cache hit rate for specified sizes of Global-Level Value Reuse Cache, and total percentage of cacheable instructions. . . . .                               | 110 |

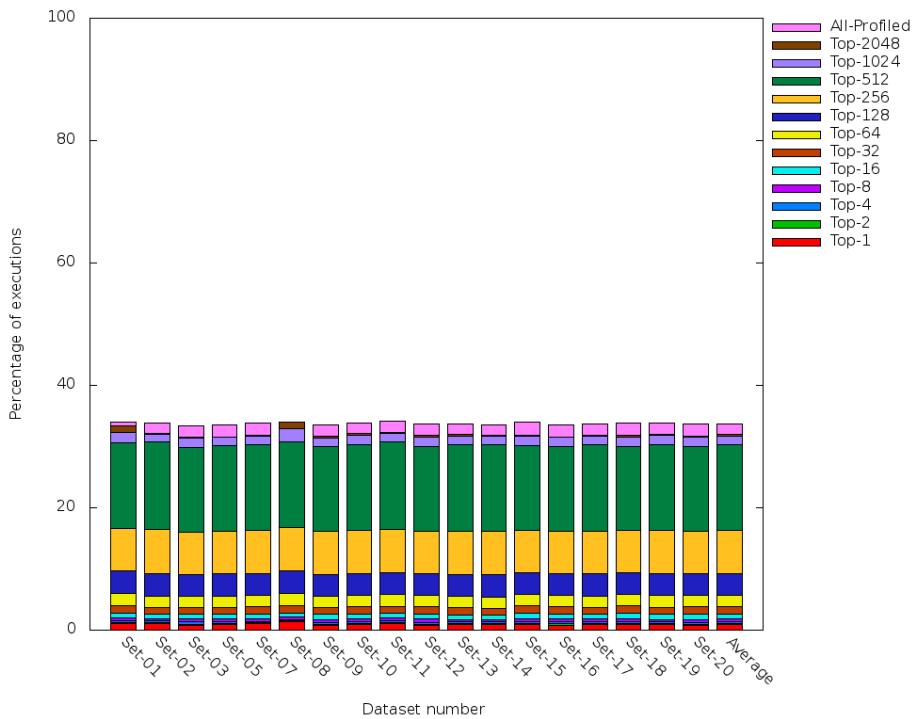

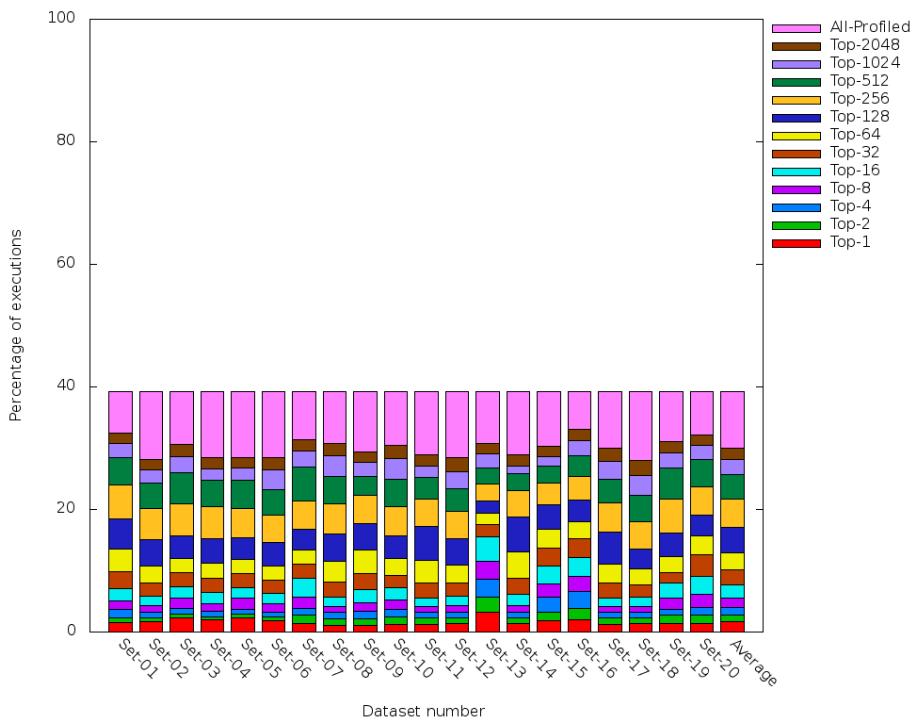

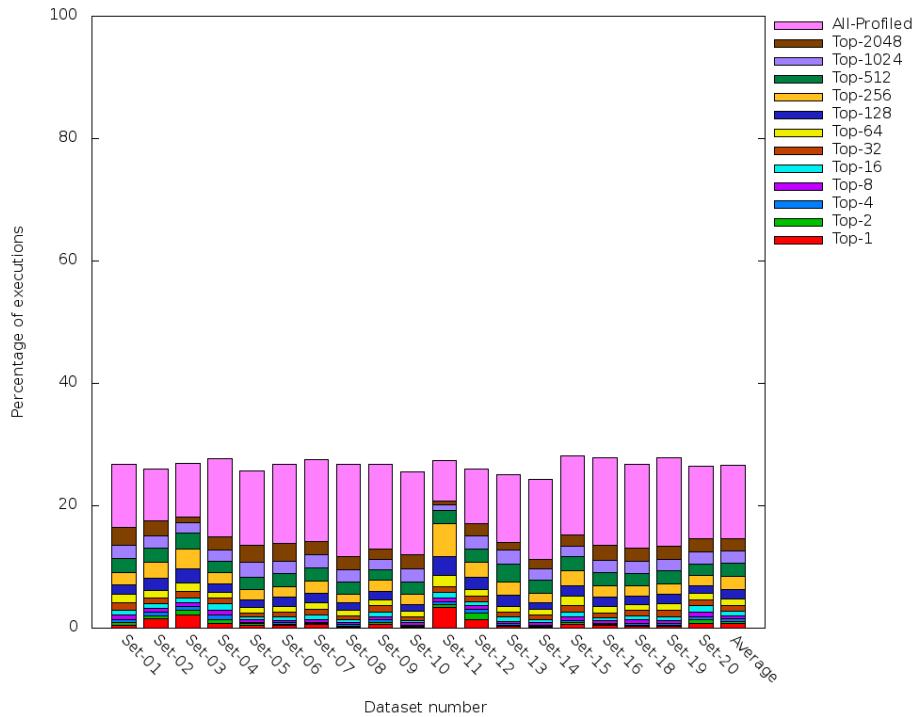

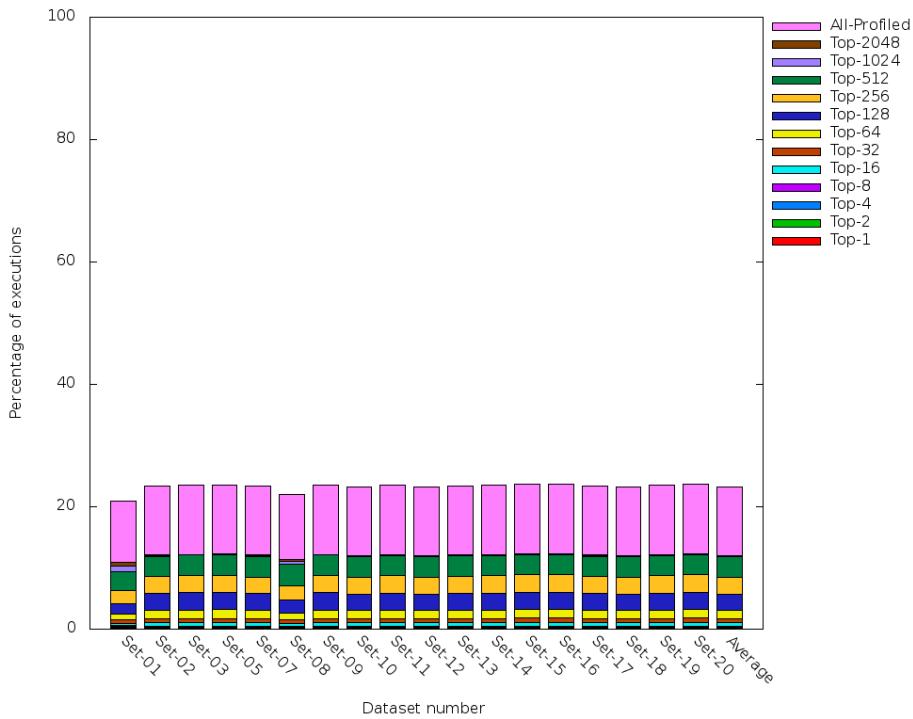

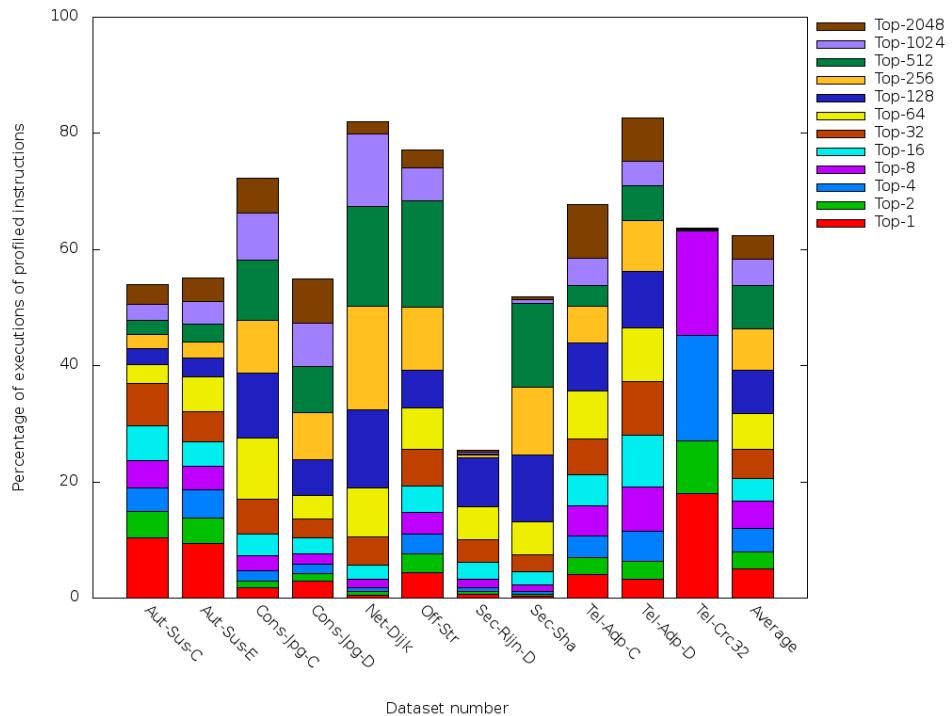

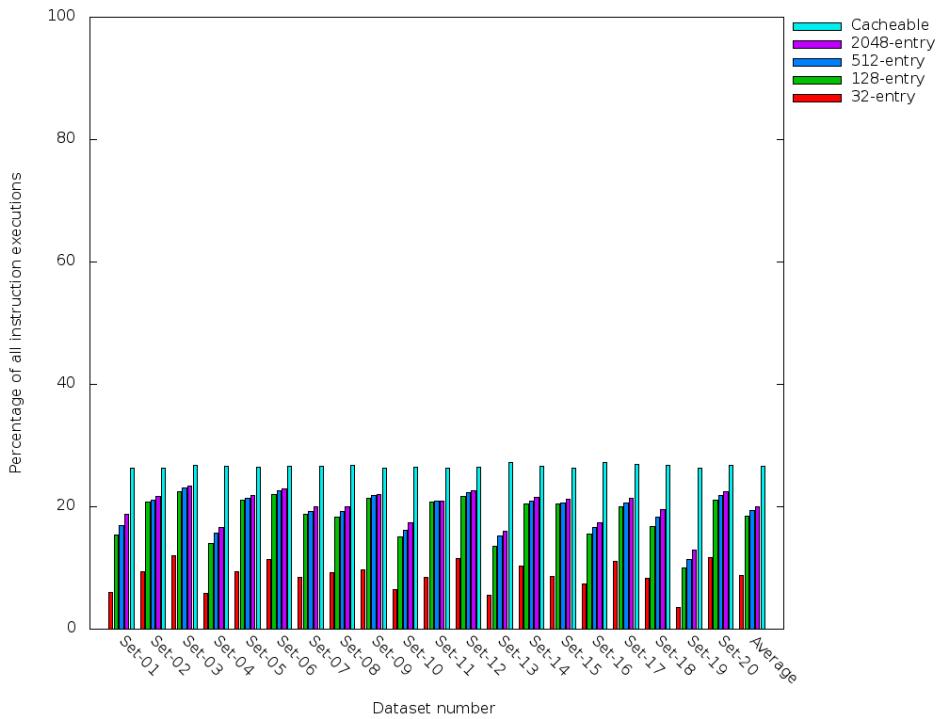

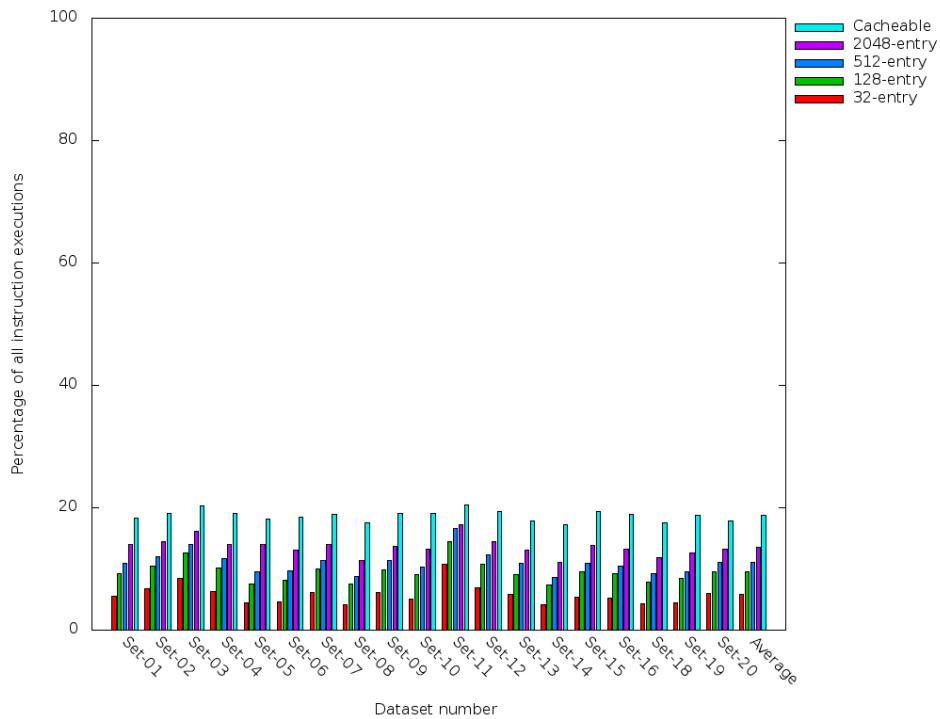

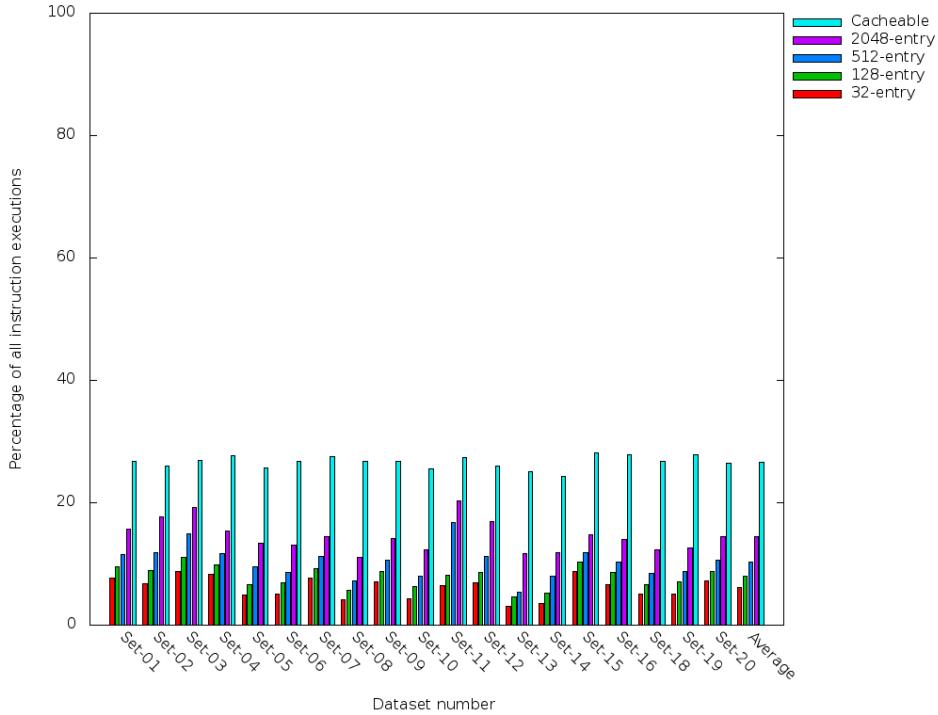

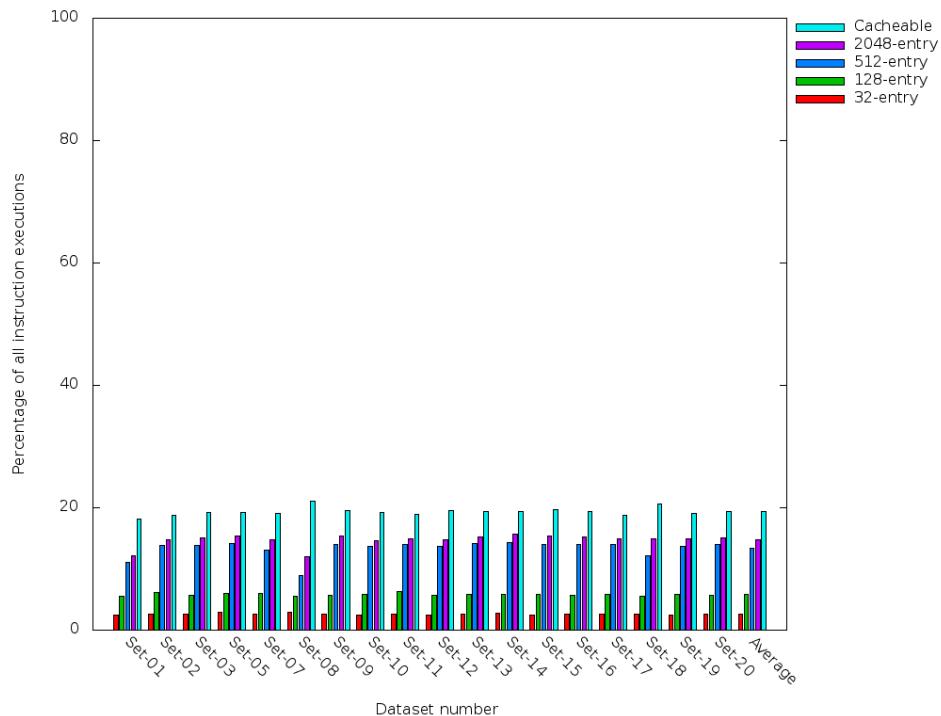

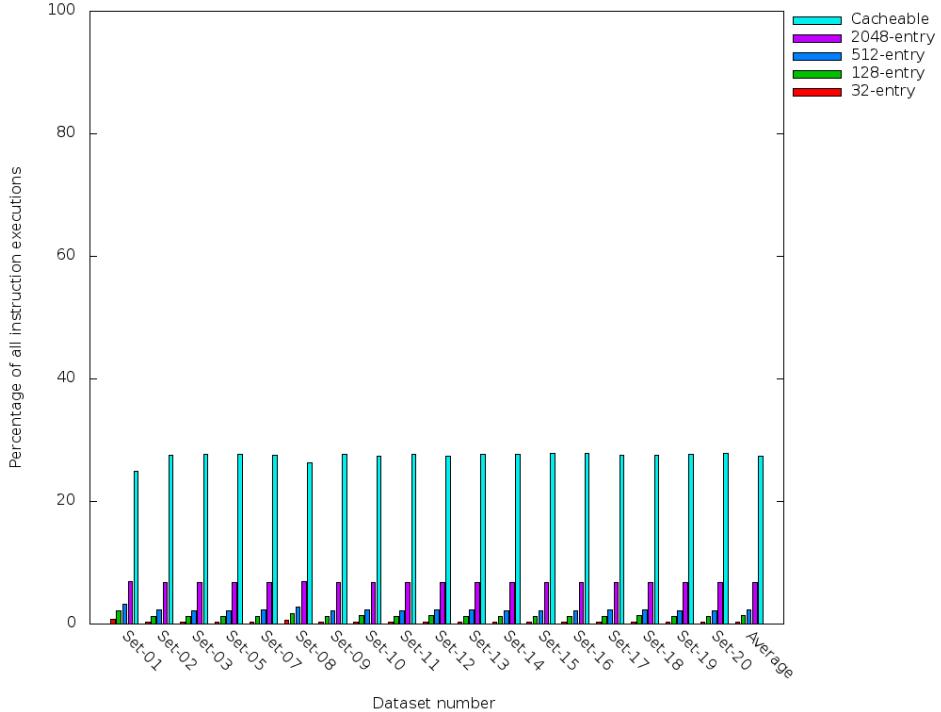

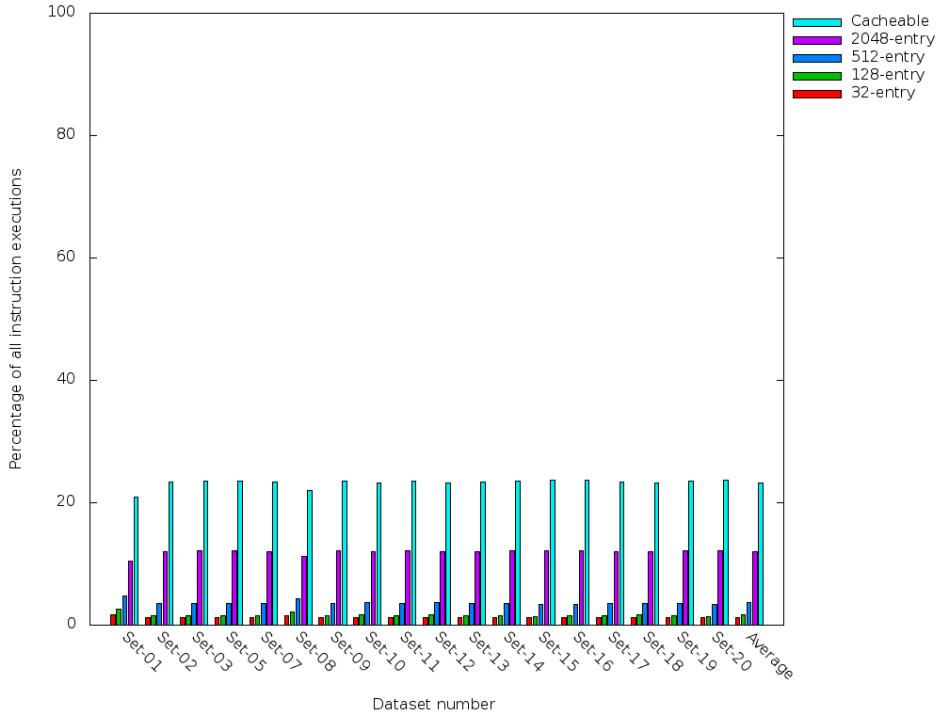

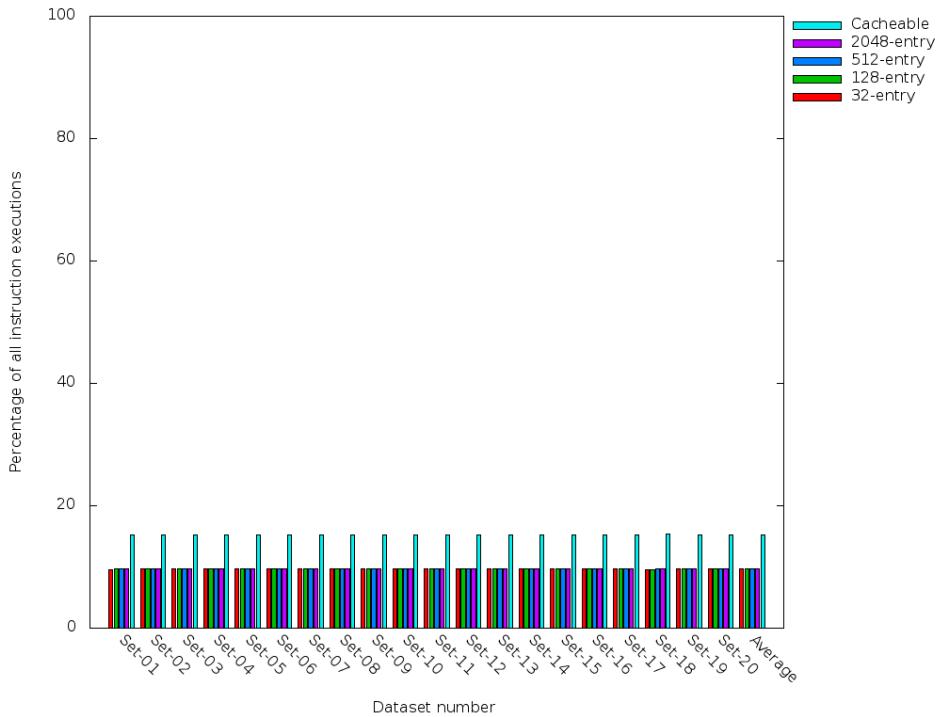

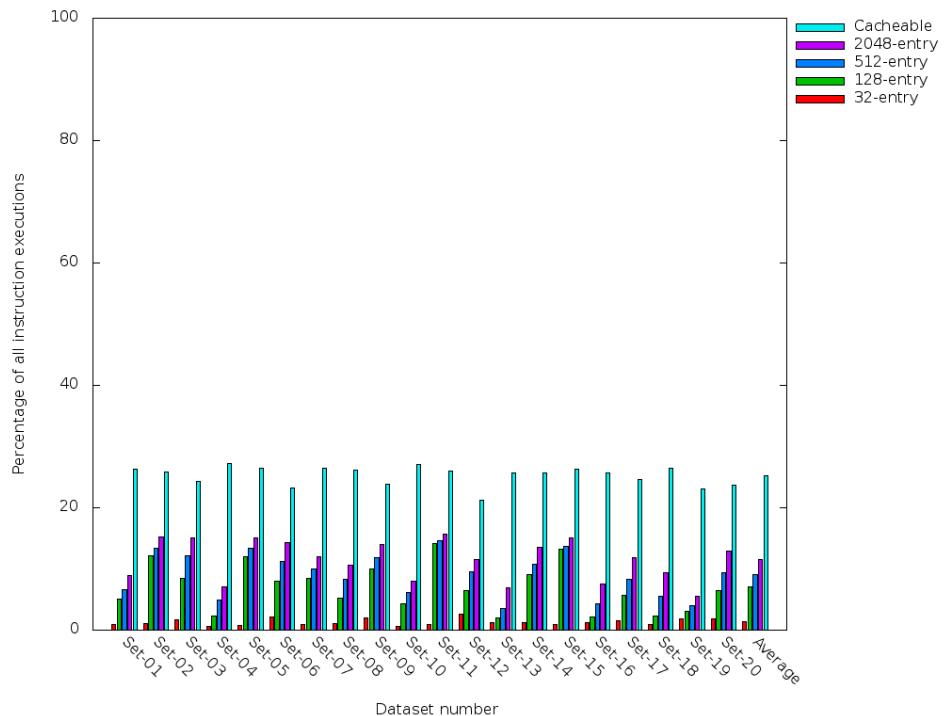

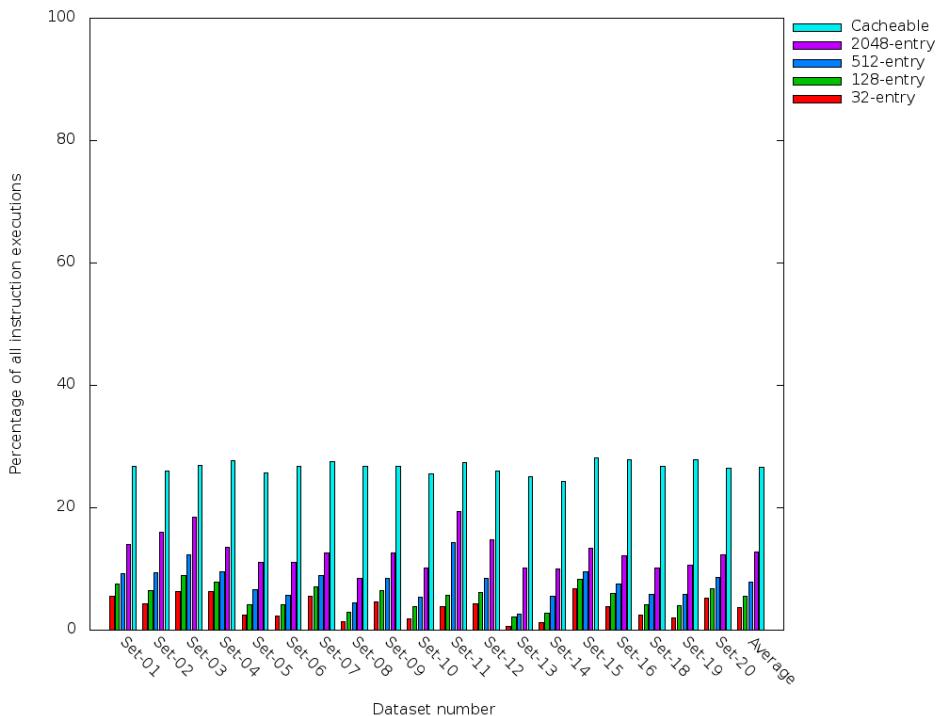

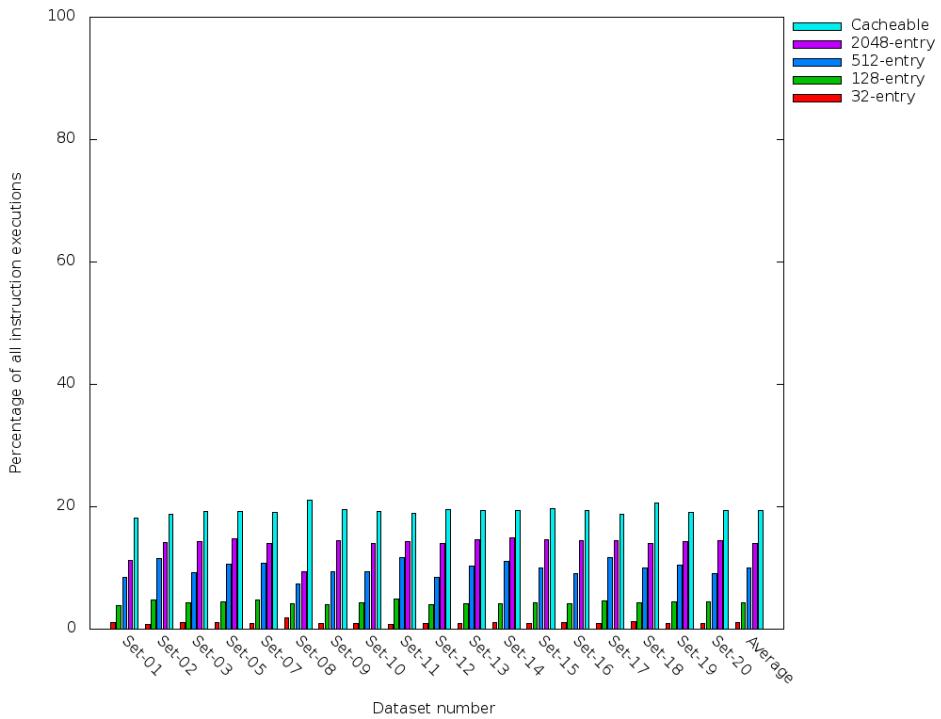

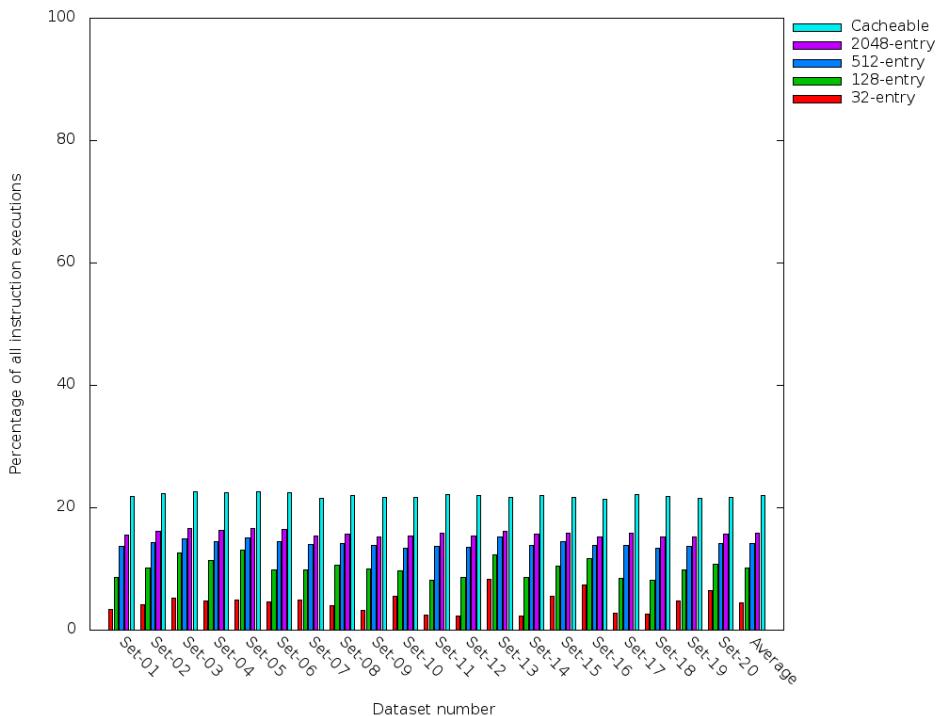

| 6.13 | Comparison of the cache hit rate for specified sizes of Global-Level Value Reuse Cache and total percentage of cacheable instructions across all benchmarks. . . . .       | 111 |

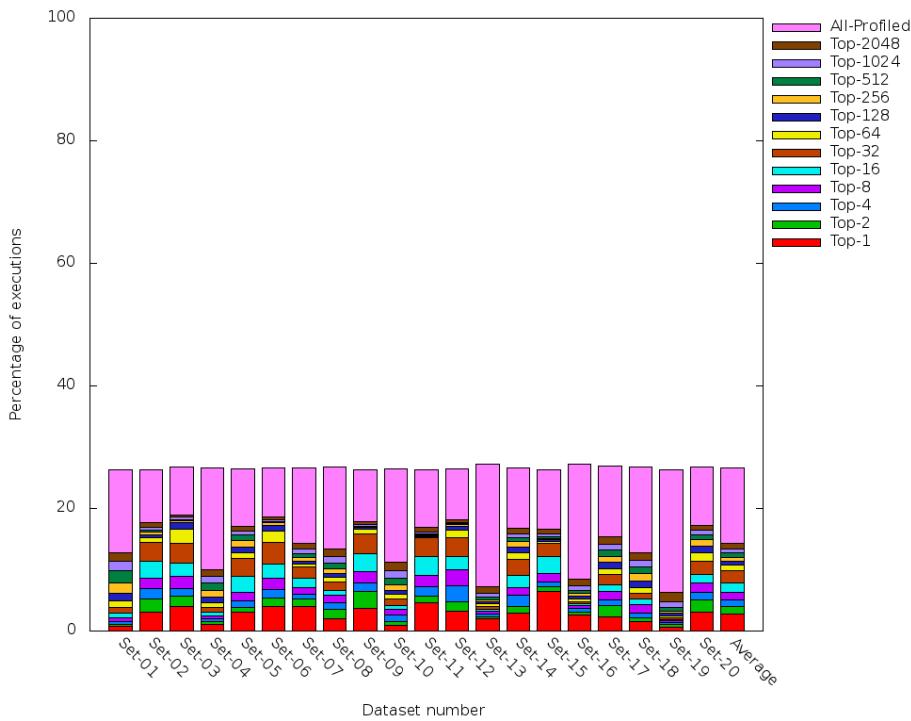

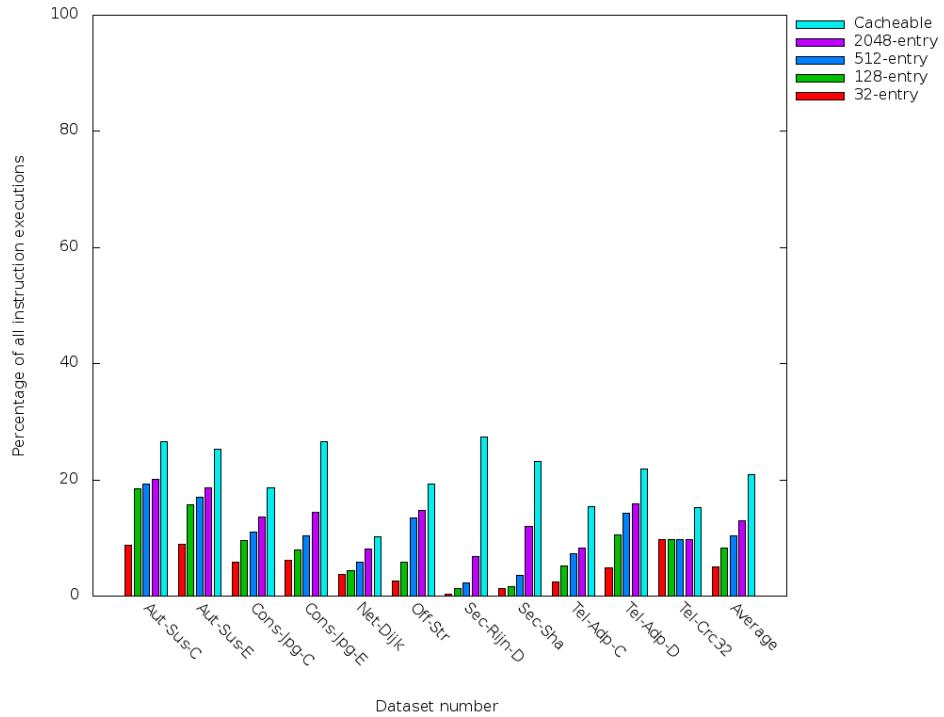

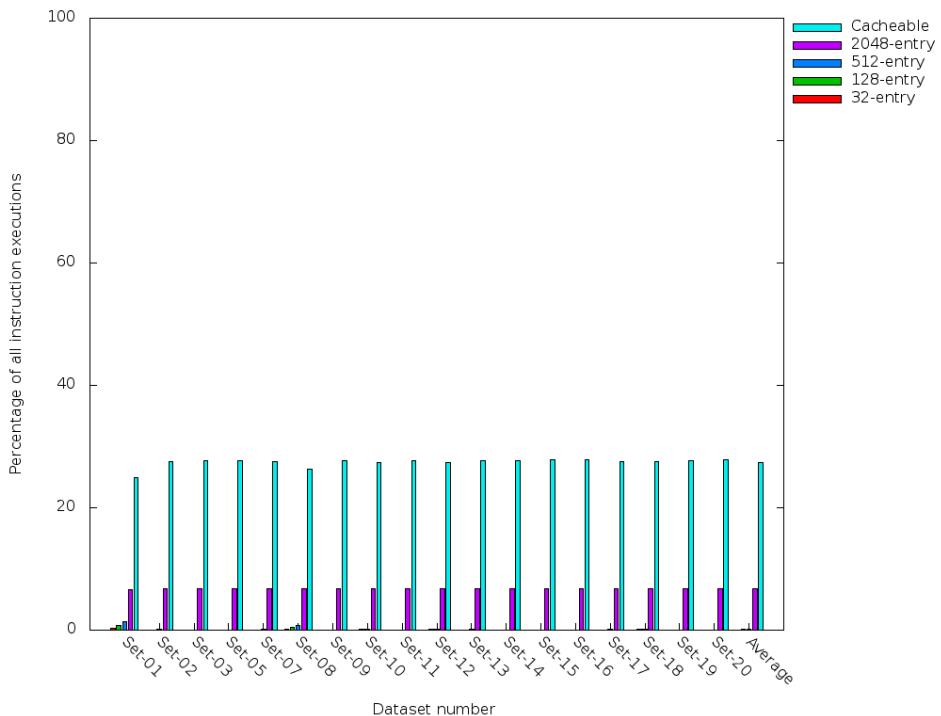

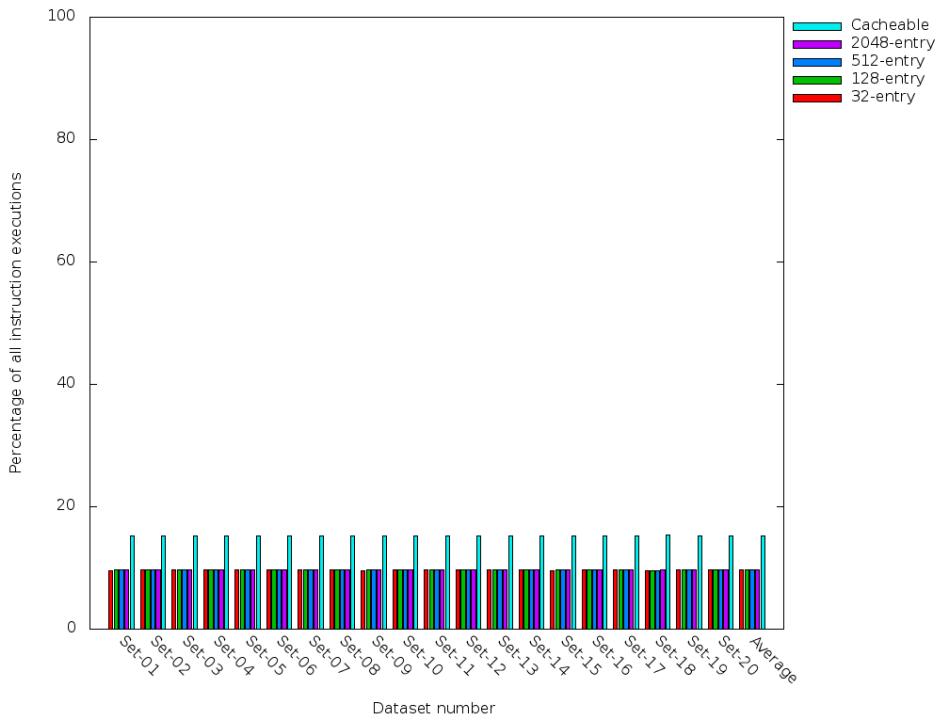

| 6.14 | Comparison of the cache hit rate for specified sizes of Global-Level Value Reuse Cache within only cacheable instructions across all benchmarks. . . . .                   | 112 |

| 6.15 | Automotive-susan-c. Cache hit rate for specified sizes of Local-Level Value Reuse Cache, and total percentage of cacheable instructions. . . . .                           | 113 |

| 6.16 | Automotive-susan-e. Cache hit rate for specified sizes of Local-Level Value Reuse Cache, and total percentage of cacheable instructions. . . . .                           | 113 |

| 6.17 | Consumer-jpeg-c. Cache hit rate for specified sizes of Local-Level Value Reuse Cache, and total percentage of cacheable instructions. . . . .                              | 114 |

| 6.18 | Consumer-jpeg-d. Cache hit rate for specified sizes of Local-Level Value Reuse Cache, and total percentage of cacheable instructions. . . . .                              | 114 |

| 6.19 | Network-dijkstra. Cache hit rate for specified sizes of Local-Level Value Reuse Cache, and total percentage of cacheable instructions. . . . .                             | 115 |

| 6.20 | Office-stringsearch. Cache hit rate for specified sizes of Local-Level Value Reuse Cache, and total percentage of cacheable instructions. . . . .                          | 116 |

|      |                                                                                                                                                                              |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.21 | Security-rijndael-d. Cache hit rate for specified sizes of Local-Level Value Reuse Cache, and total percentage of cacheable instructions. . . . .                            | 116 |

| 6.22 | Security-sha. Cache hit rate for specified sizes of Local-Level Value Reuse Cache, and total percentage of cacheable instructions. . . . .                                   | 117 |

| 6.23 | Telecom-adpcm-c. Cache hit rate for specified sizes of Local-Level Value Reuse Cache, and total percentage of cacheable instructions. . . . .                                | 118 |

| 6.24 | Telecom-adpcm-d. Cache hit rate for specified sizes of Local-Level Value Reuse Cache, and total percentage of cacheable instructions. . . . .                                | 118 |

| 6.25 | Telecom-crc32. Cache hit rate for specified sizes of Local-Level Value Reuse Cache, and total percentage of cacheable instructions. . . . .                                  | 119 |

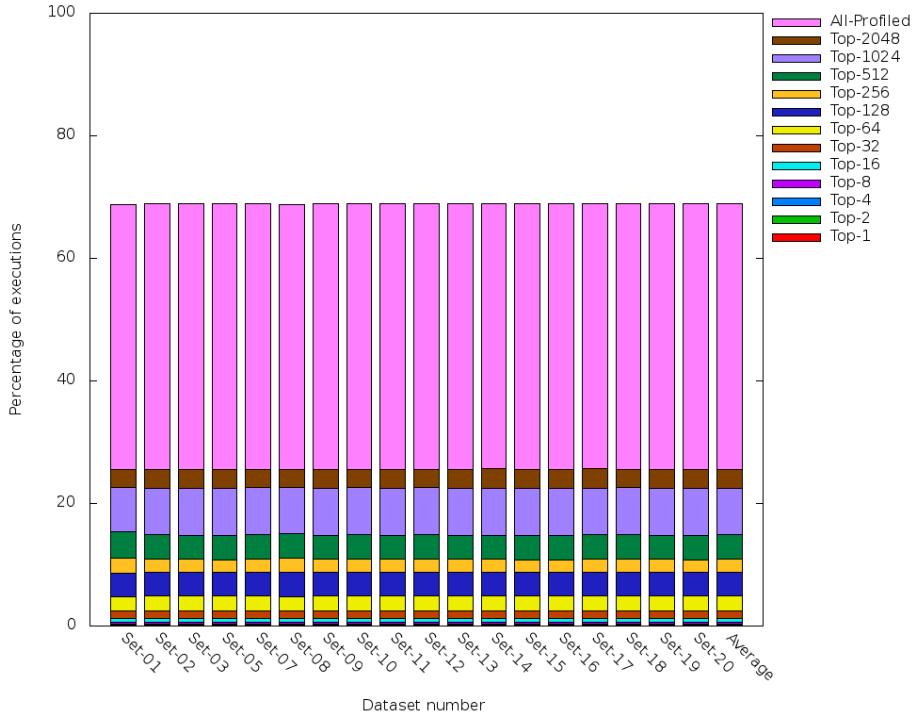

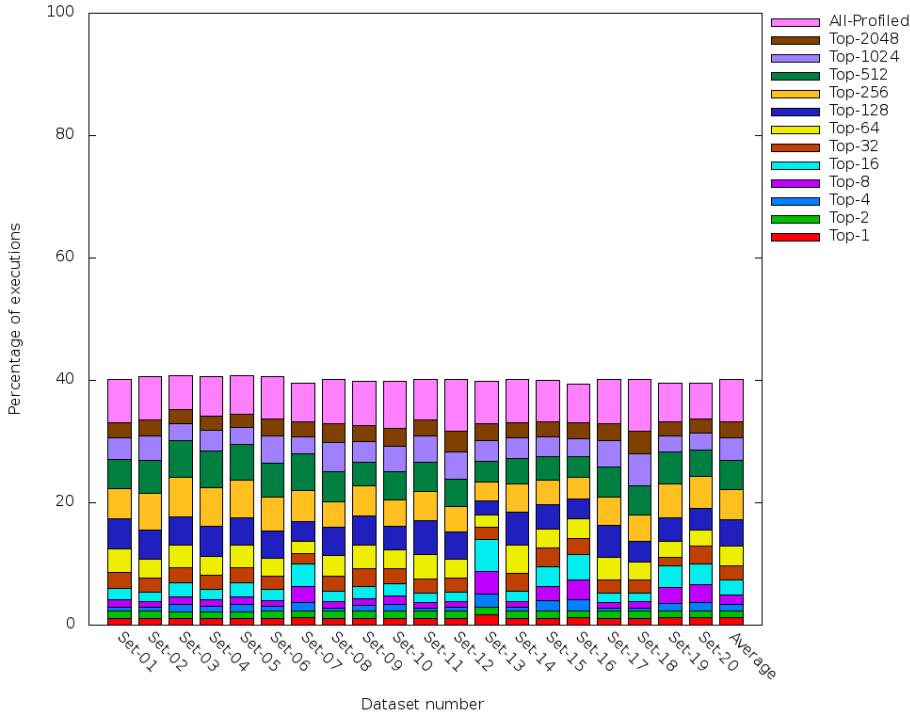

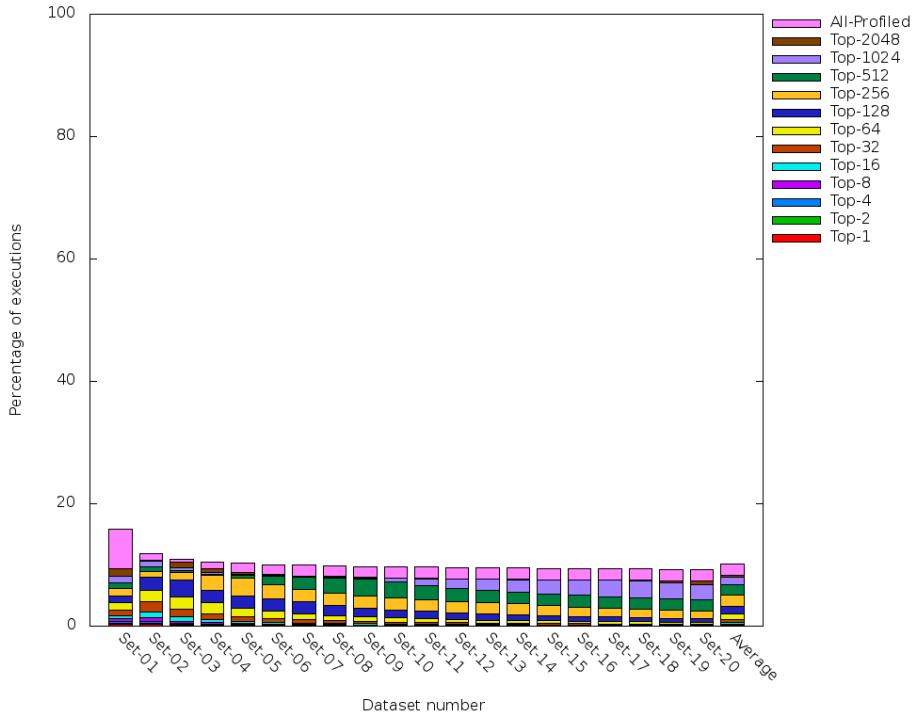

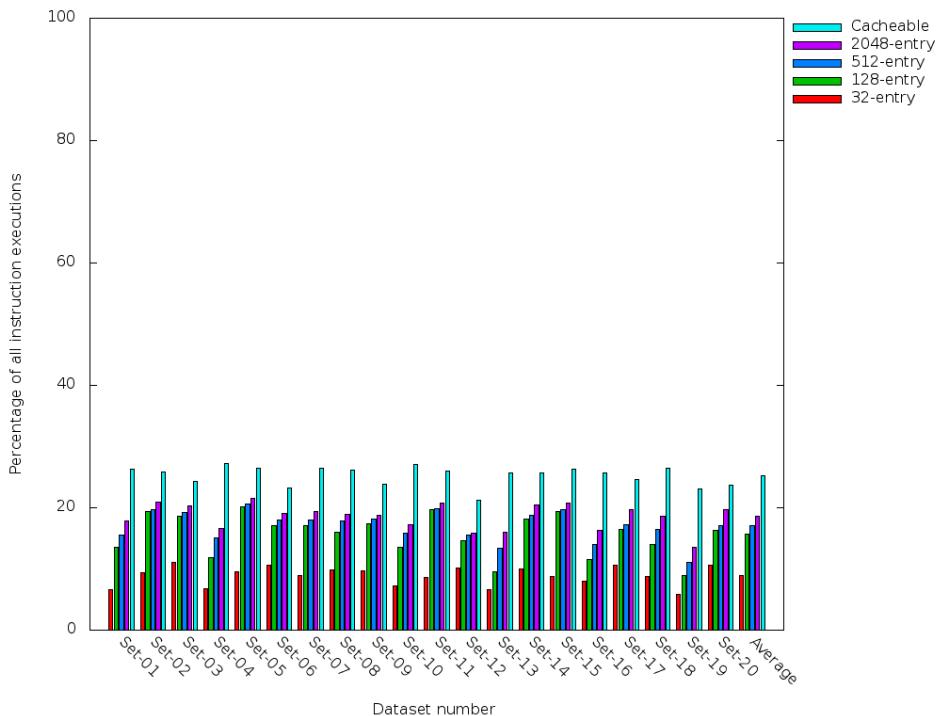

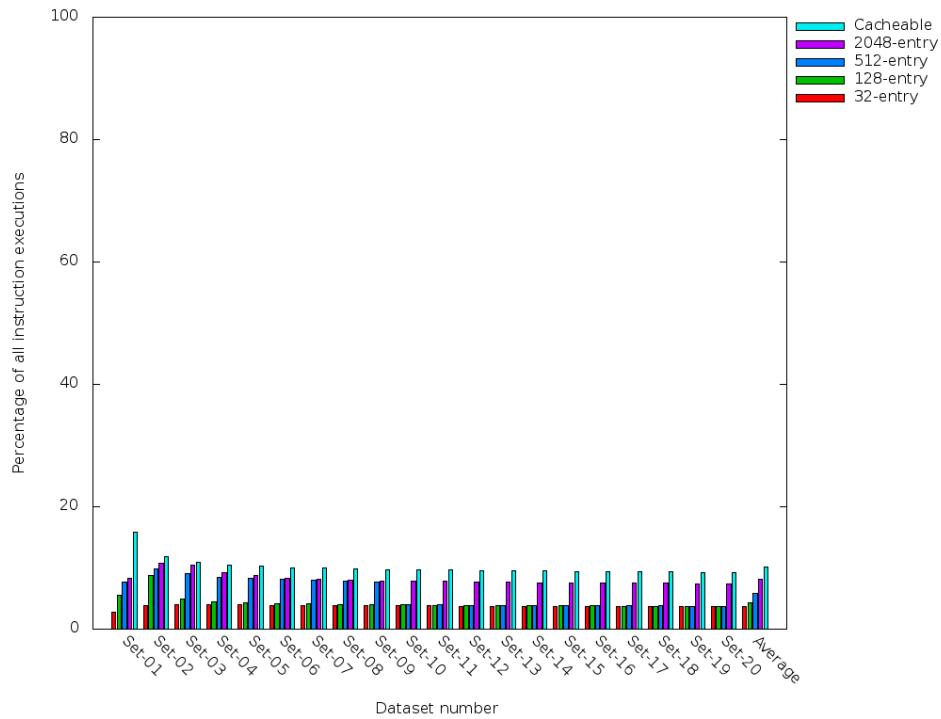

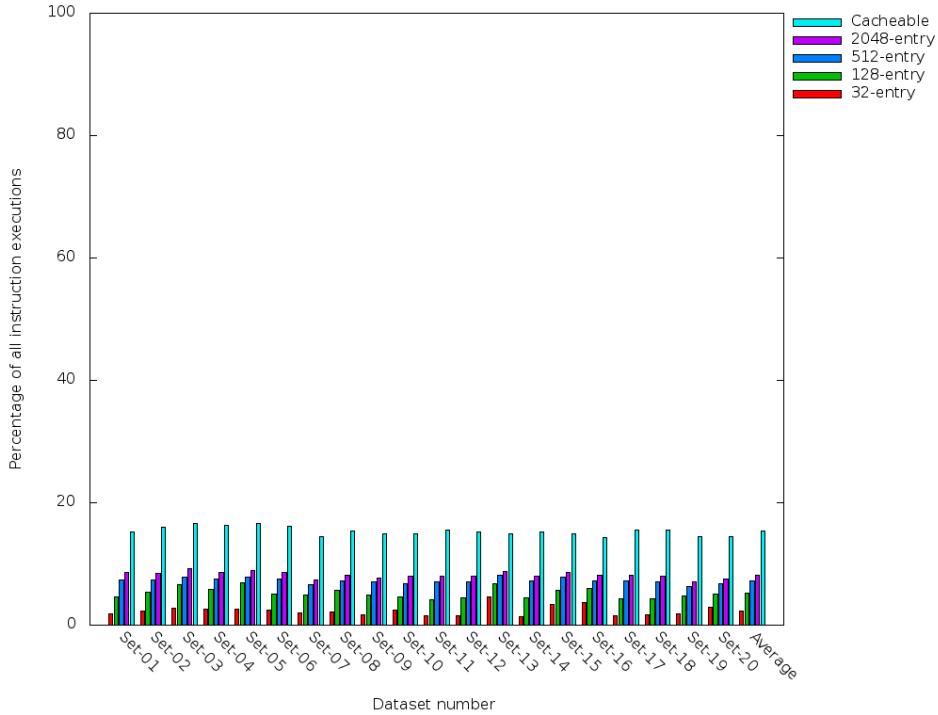

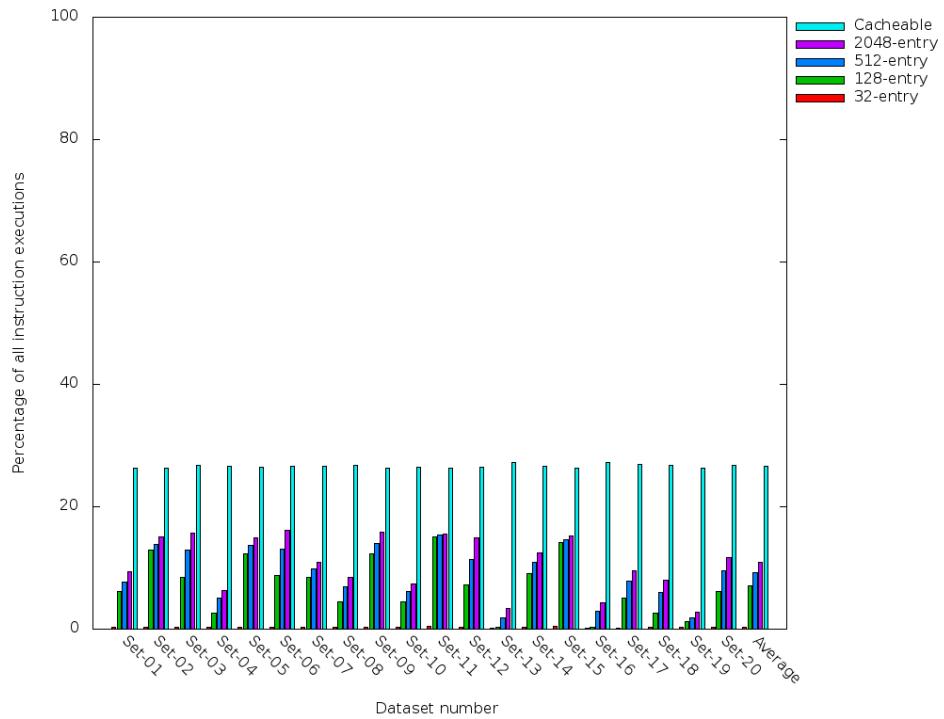

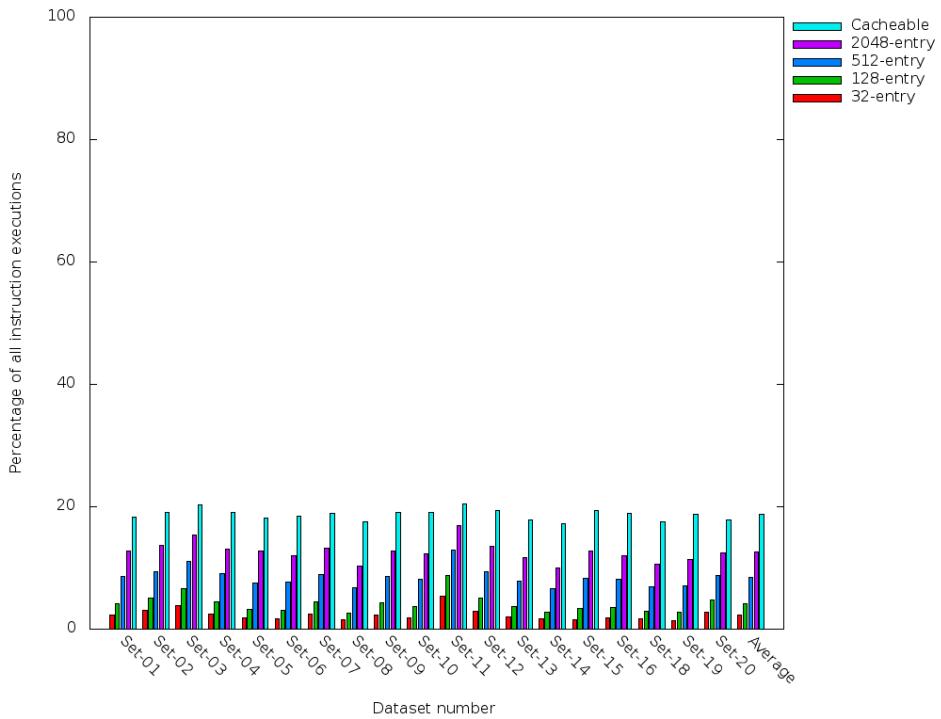

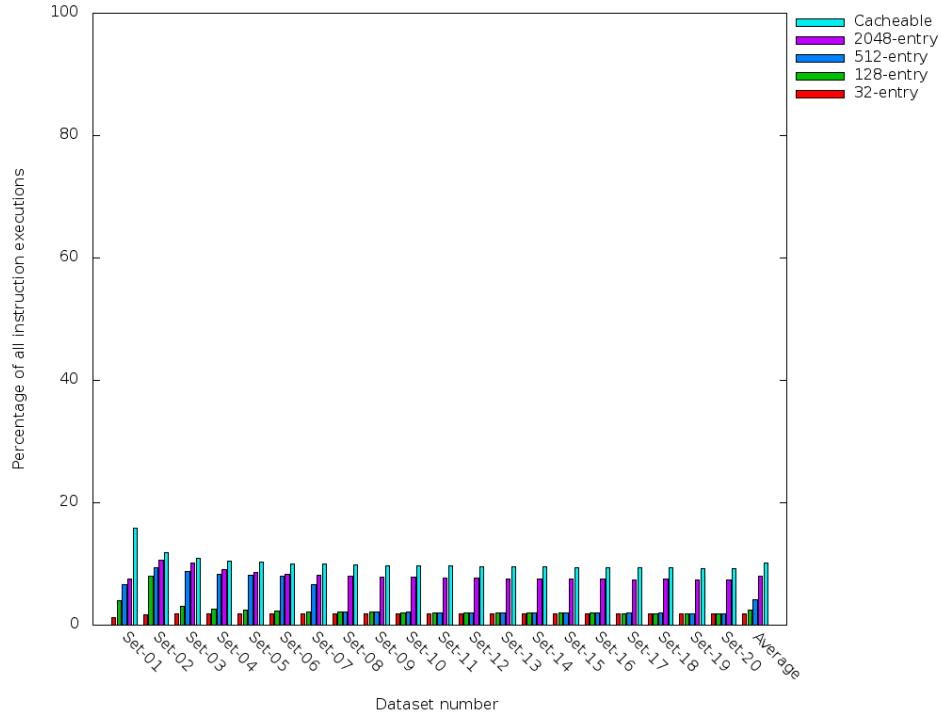

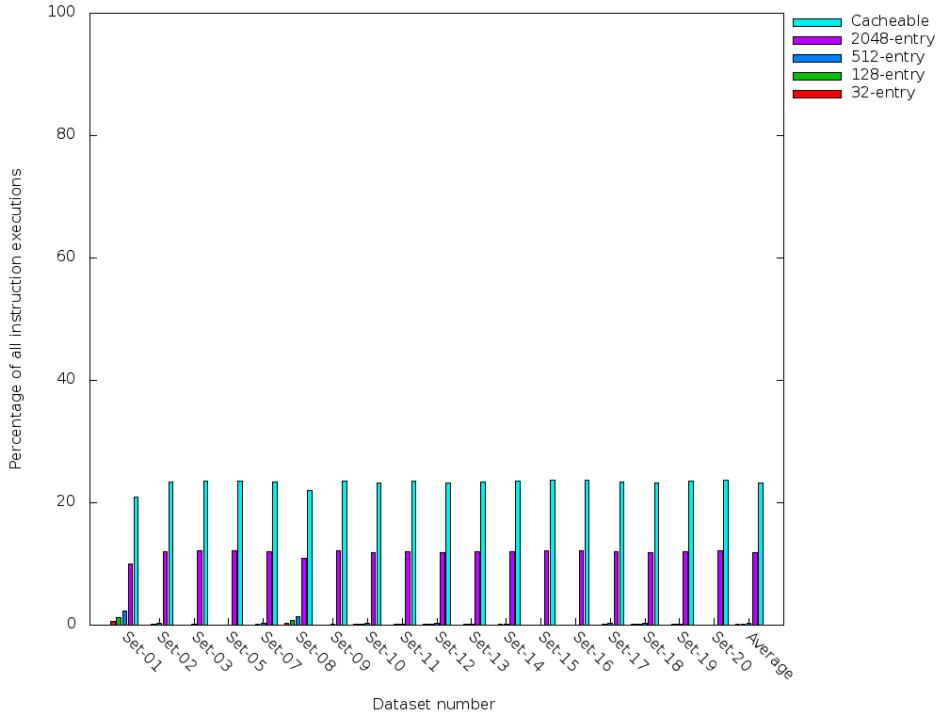

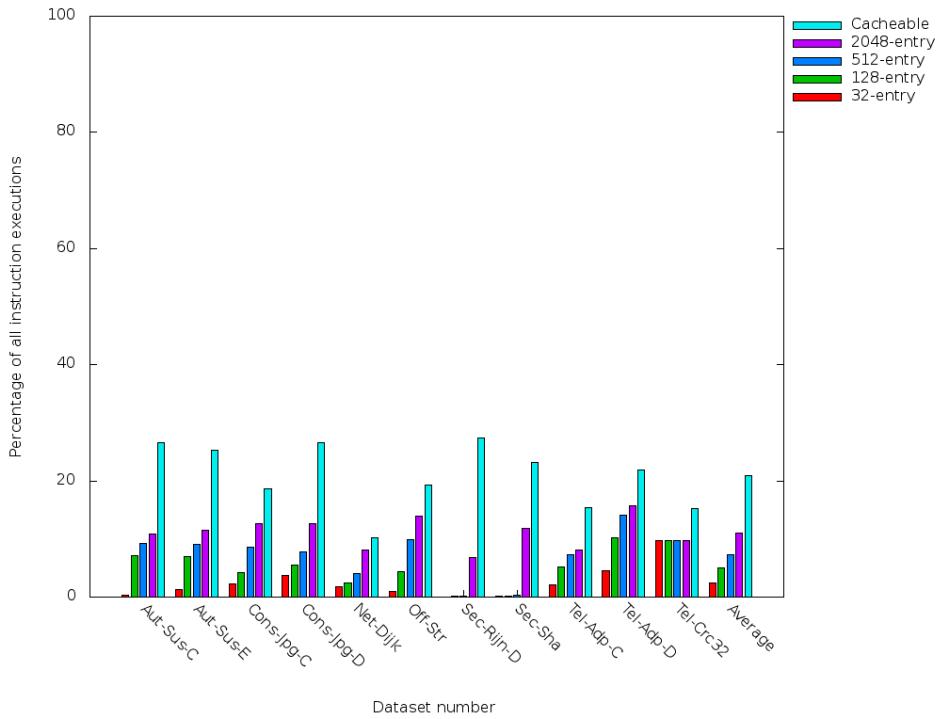

| 6.26 | Comparison of the cache hit rate for specified sizes of Local-Level Value Reuse Cache and total percentage of cacheable instructions across all benchmarks. . . . .          | 119 |

| 7.1  | Automotive-susan-c. Percentage of all memory accesses accounted for by the top N most frequently transferred values when a cache is implemented. . . . .                     | 124 |

| 7.2  | Automotive-susan-e. Percentage of all memory accesses accounted for by the top N most frequently transferred values when a cache is implemented. . . . .                     | 125 |

| 7.3  | Consumer-Jpeg-C. Percentage of all memory accesses accounted for by the top N most frequently transferred values when a cache is implemented. . . . .                        | 125 |

| 7.4  | Consumer-Jpeg-D. Percentage of all memory accesses accounted for by the top N most frequently transferred values when a cache is implemented. . . . .                        | 126 |

| 7.5  | Network-Dijkstra. Percentage of all memory accesses accounted for by the top N most frequently transferred values when a cache is implemented. . . . .                       | 127 |

| 7.6  | Office-Stringsearch. Percentage of all memory accesses accounted for by the top N most frequently transferred values when a cache is implemented. . . . .                    | 127 |

| 7.7  | Security-Rijndael-D. Percentage of all memory accesses accounted for by the top N most frequently transferred values when a cache is implemented. . . . .                    | 128 |

| 7.8  | Security-Sha. Percentage of all memory accesses accounted for by the top N most frequently transferred values when a cache is implemented. . . . .                           | 129 |

| 7.9  | Telecom-Adpcm-C. Percentage of all memory accesses accounted for by the top N most frequently transferred values when a cache is implemented. . . . .                        | 129 |

| 7.10 | Telecom-Adpcm-D. Percentage of all memory accesses accounted for by the top N most frequently transferred values when a cache is implemented. . . . .                        | 130 |

| 7.11 | Telecom-Crc32. Percentage of all memory accesses accounted for by the top N most frequently transferred values when a cache is implemented. . . . .                          | 131 |

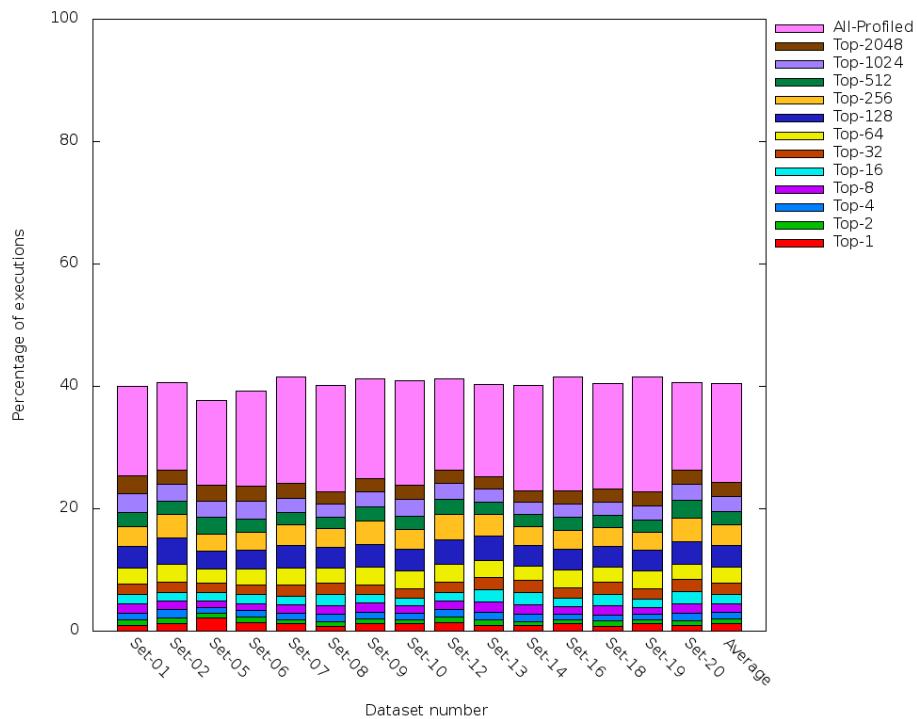

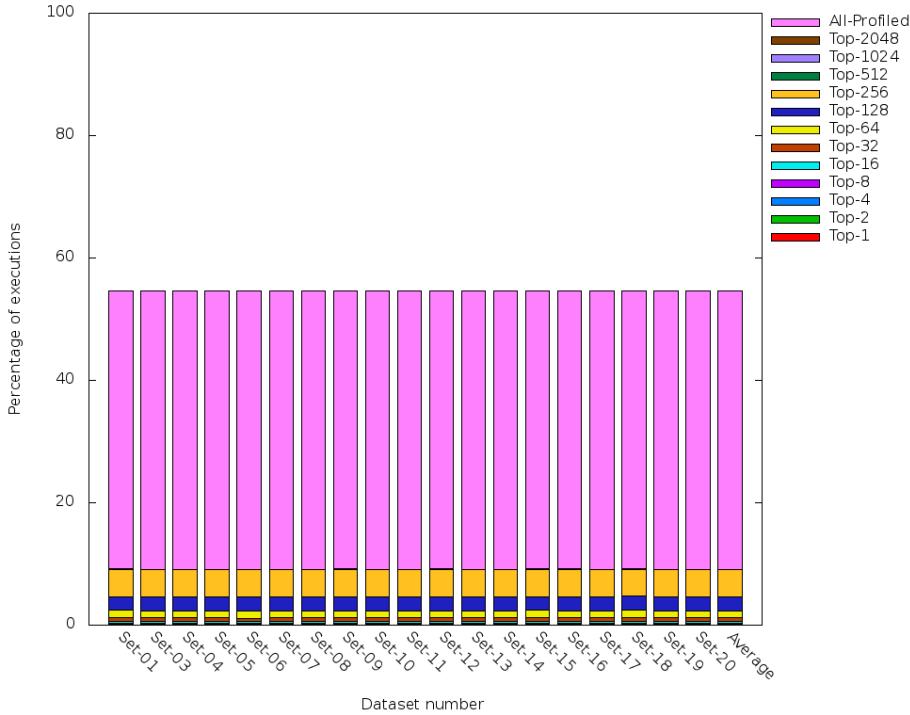

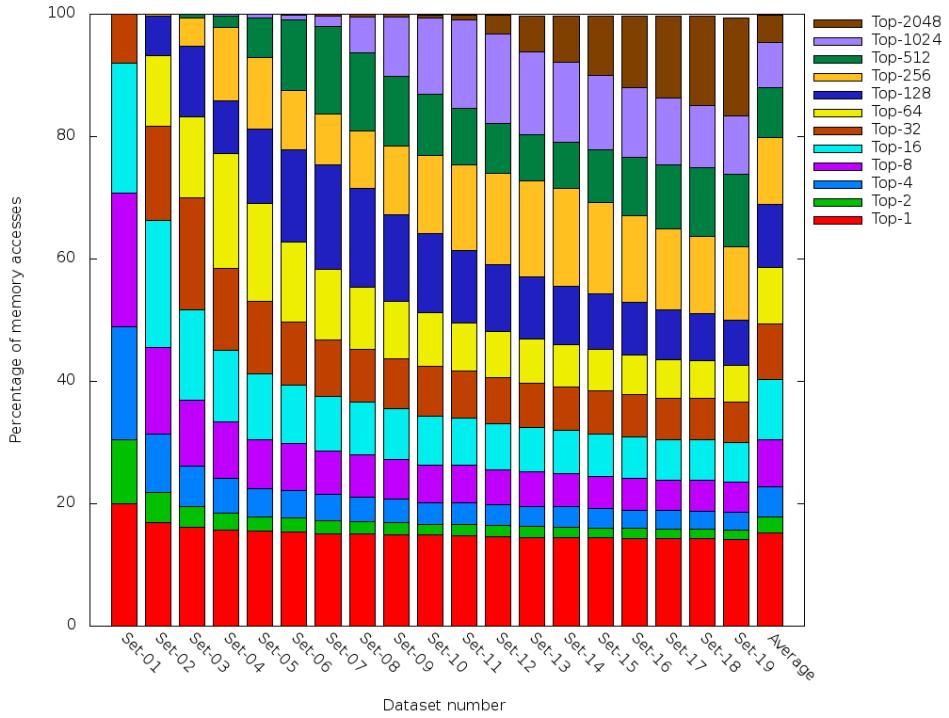

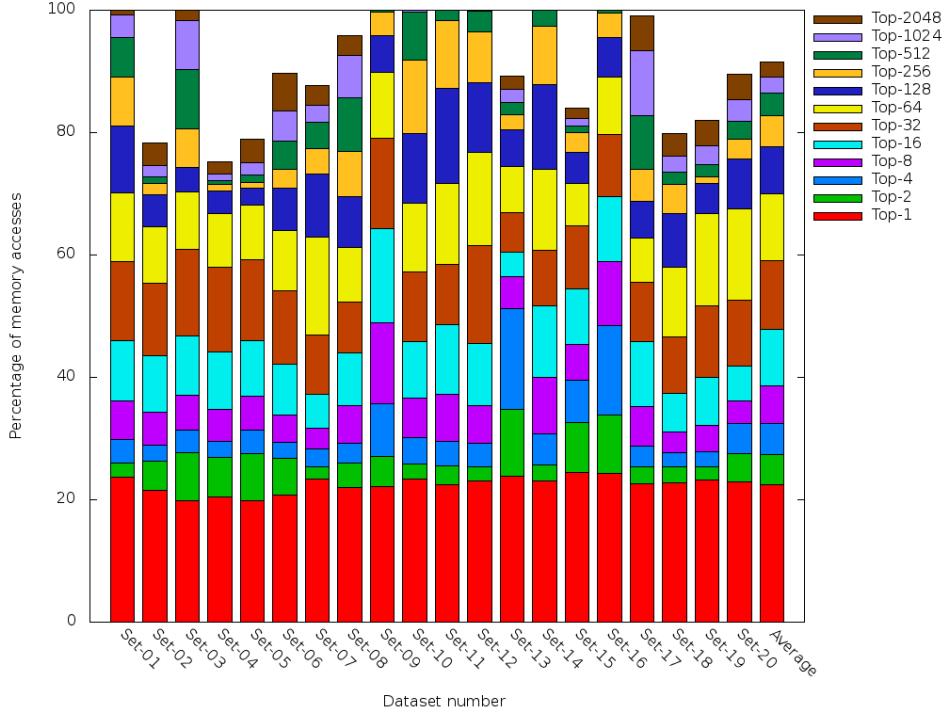

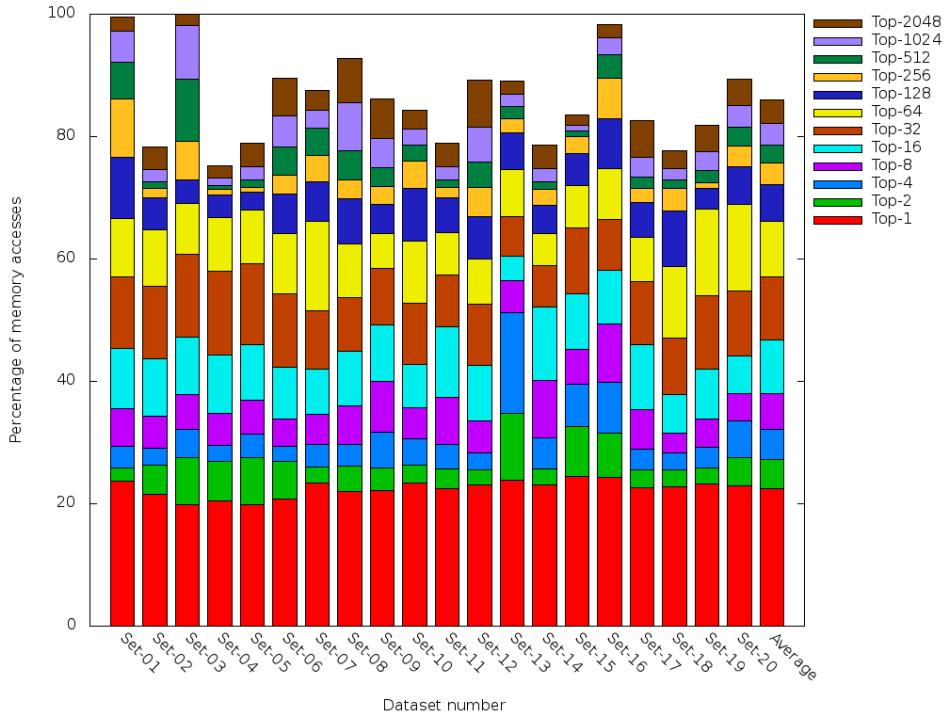

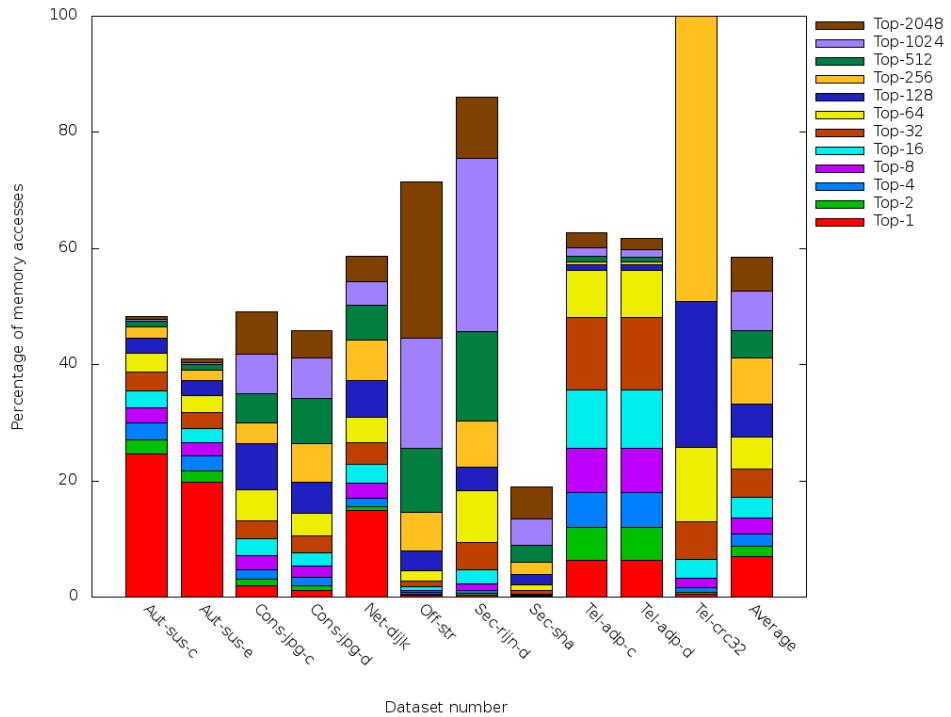

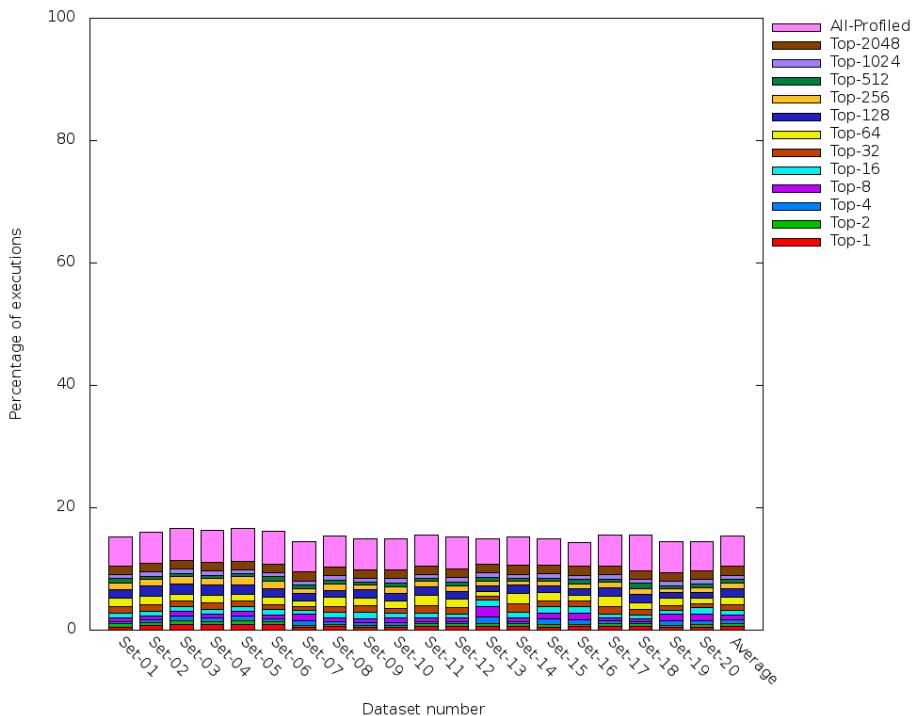

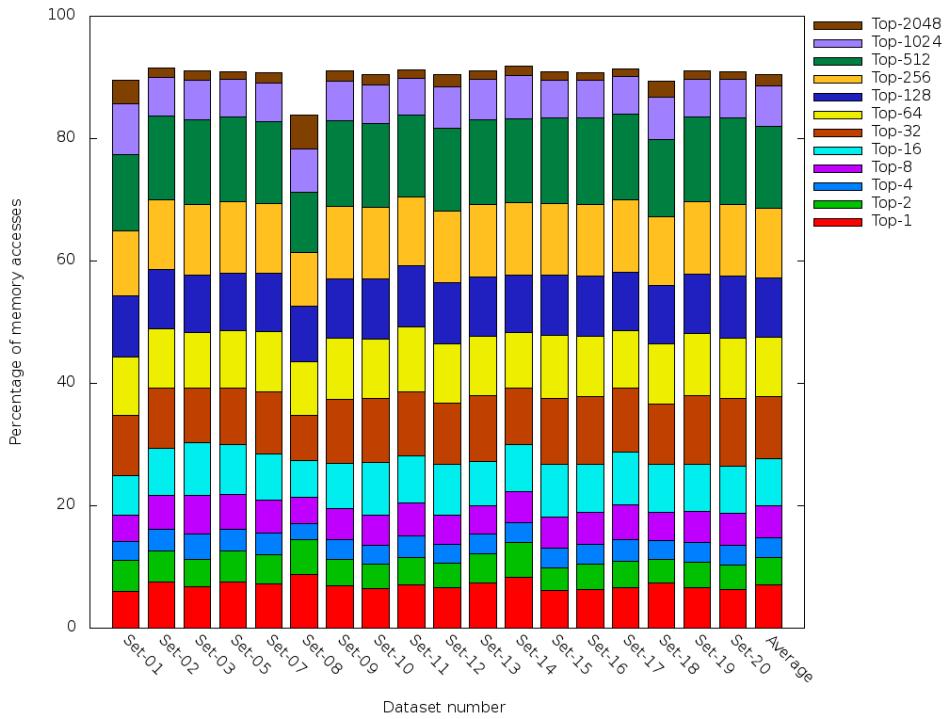

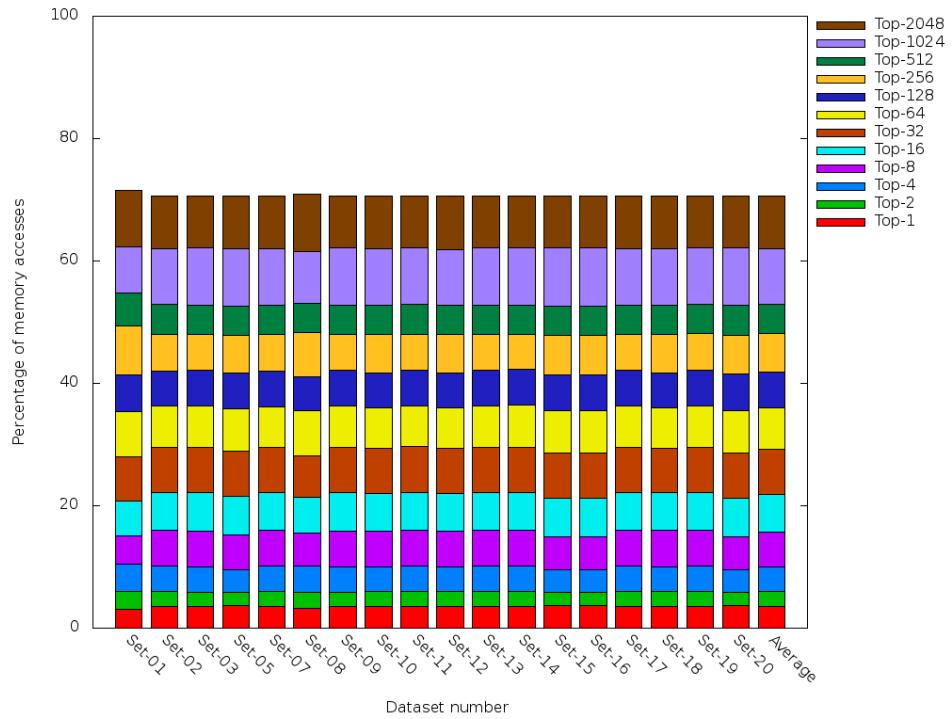

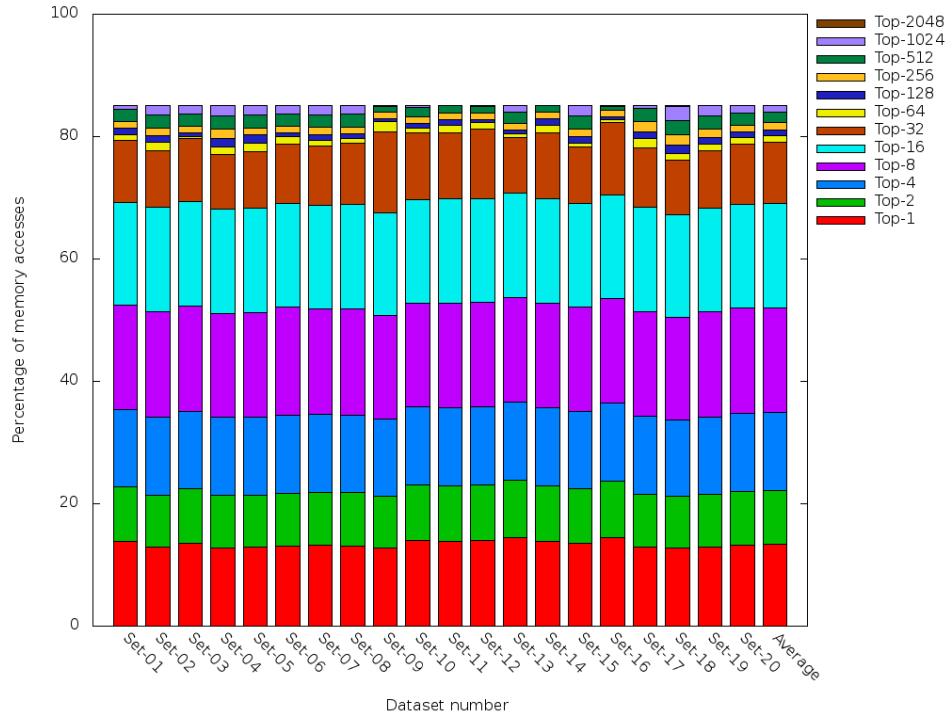

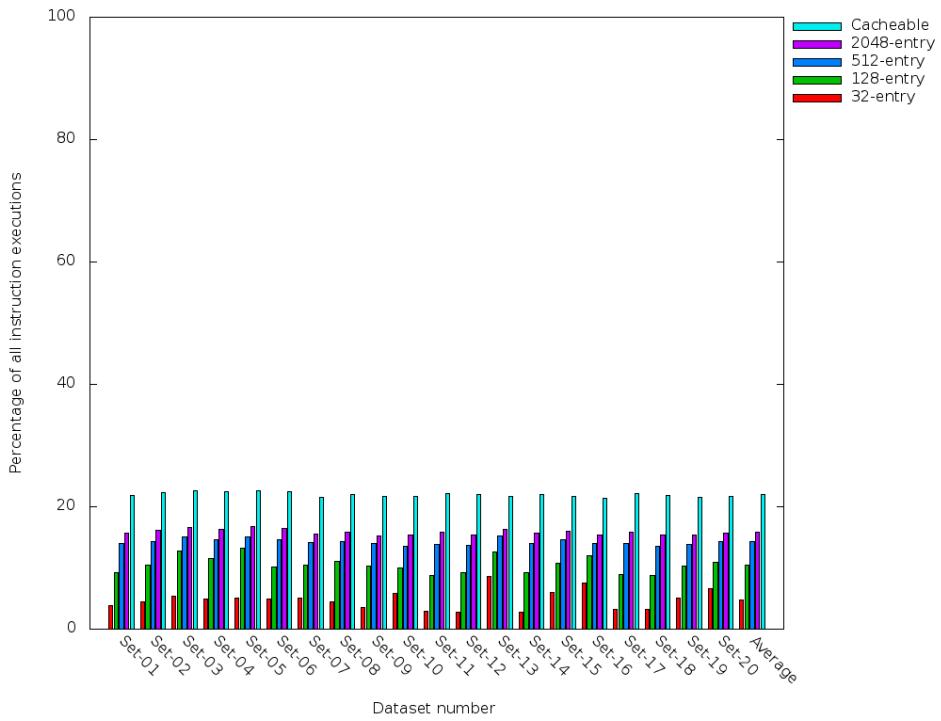

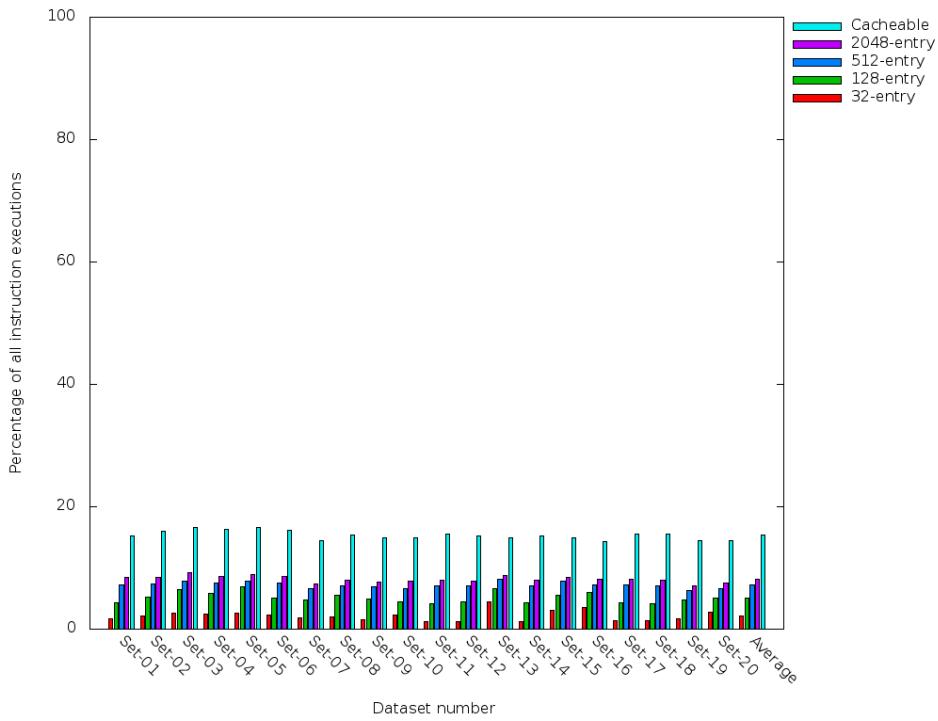

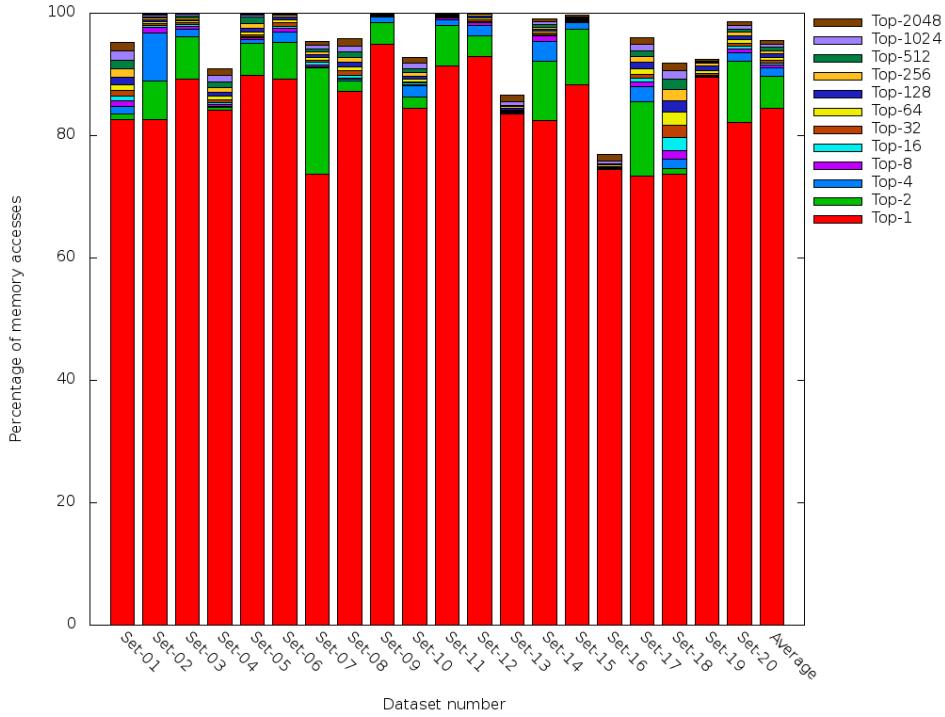

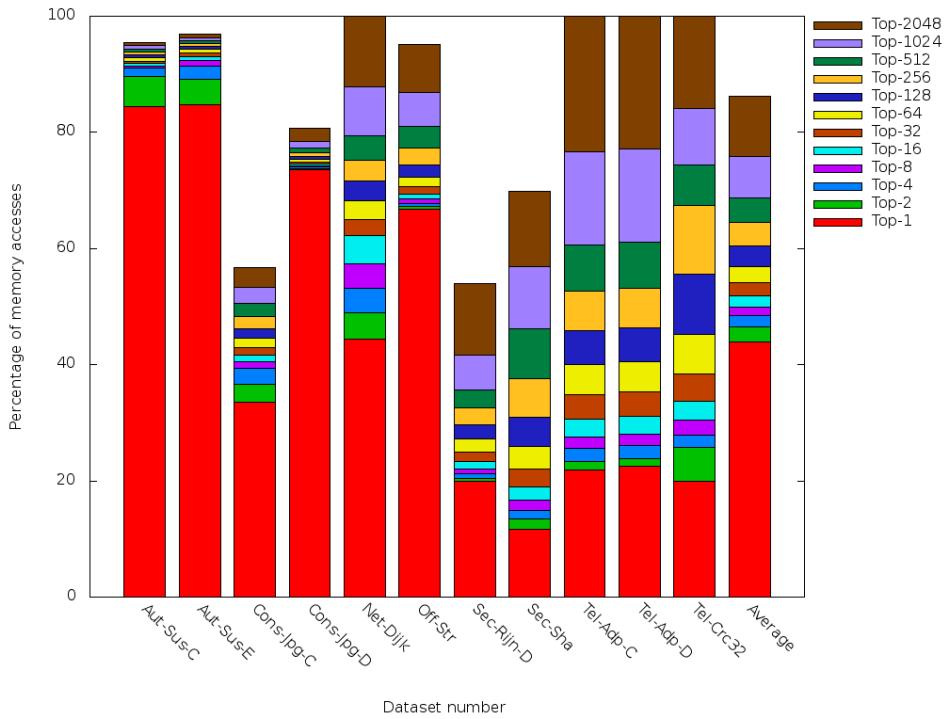

| 7.12 | Comparison of the percentage of all memory accesses accounted for by the top N most frequently transferred values when a cache is implemented across all benchmarks. . . . . | 131 |

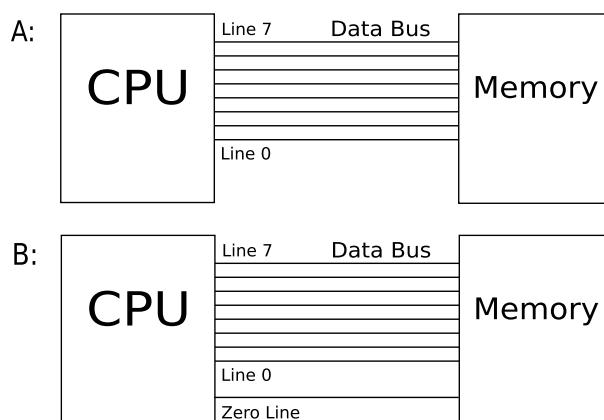

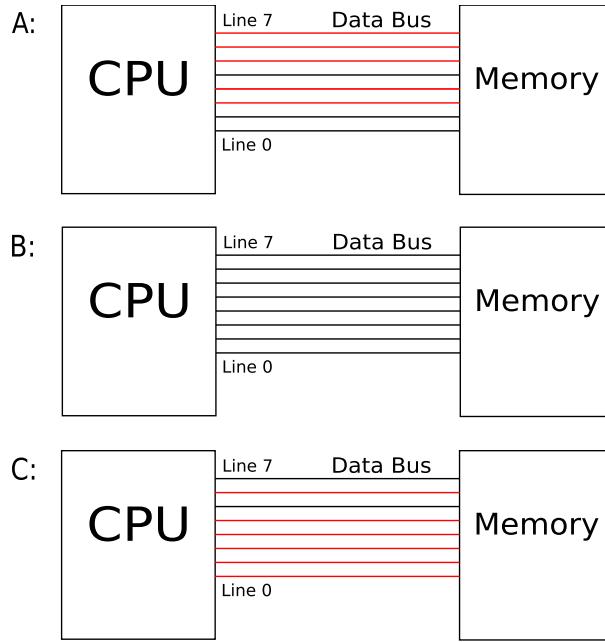

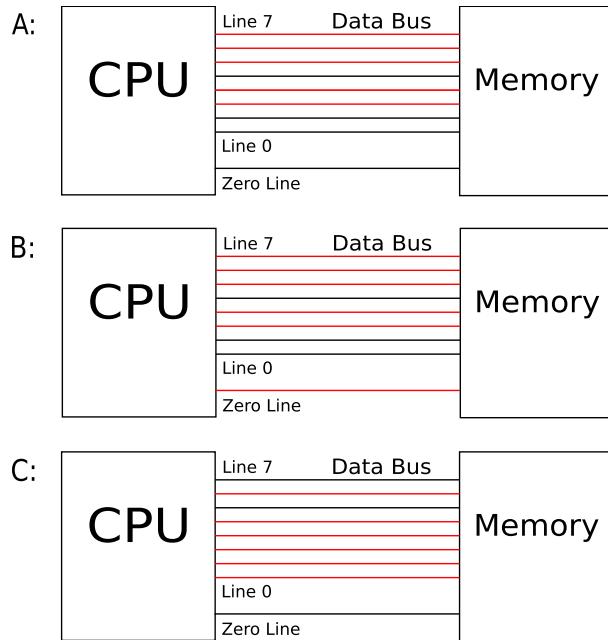

| 7.13 | An 8-bit data bus. A: Without zero line. B: With zero line. . . . .                                                                                                          | 132 |

| 7.14 | Three values transferred on an unmodified bus. Red represents a line switched on, black switched off. A: &EC transferred. B: &0 transferred. C: &5F transferred. . . . .     | 133 |

| 7.15 | Three values transferred on a modified bus. Red represents a line switched on, black switched off. A: &EC transferred. B: &0 transferred. C: &5F transferred. . . . .        | 134 |

# List of Tables

|      |                                                                                                 |     |

|------|-------------------------------------------------------------------------------------------------|-----|

| 4.1  | Instructions which will be profiled on LLVM for Instruction-level Value Profiling. . . . .      | 25  |

| 4.2  | Instructions which will not be profiled on LLVM for Instruction-level Value Profiling . . . . . | 25  |

| 4.3  | Instructions which will be profiled on the x86 architecture. . . . .                            | 25  |

| 4.4  | Functions which perform the execution of opcode in the LLVM Interpreter. . . . .                | 30  |

| 4.5  | Testing of Global-level Instruction Profiling on LLVM . . . . .                                 | 36  |

| 4.6  | Testing of Global-level Memory Profiling on LLVM . . . . .                                      | 37  |

| 4.7  | Testing of Local-level Memory Profiling on LLVM . . . . .                                       | 39  |

| 4.8  | Testing of Global-level Instruction Profiling on the x86 Architecture . . . . .                 | 41  |

| 4.9  | Testing of Global-level Memory Profiling on the x86 Architecture . . . . .                      | 42  |

| 4.10 | Testing of Local-level Memory Profiling on the x86 Architecture . . . . .                       | 44  |

| 6.1  | Testing of Global-level 8-entry Value Reuse Cache . . . . .                                     | 98  |

| 6.2  | Testing of Local-level 8-entry Value Reuse Cache . . . . .                                      | 99  |

| 6.3  | Testing of Global-level 2-entry Value Reuse Cache . . . . .                                     | 101 |

# Chapter 1

## Introduction

### 1.1 What is Value Profiling?

Computations in an executing program have a set of live inputs and live outputs. Live inputs are the inputs used by the computation. Live outputs are the variables which the computation can potentially write to and modify.

*Value profiling* is the recording of live inputs and outputs of computations during the execution of the program. At the end of the execution, all the data recorded constitutes the *value profile* for the execution of the program. The granularity of a computation may vary. At the smallest scale, a single instruction can be regarded as a computation. In this case, the inputs of the computation may be the instruction's operands, the current state of some of the registers/flags, or memory locations. The outputs of the computation may be registers, flags or memory locations.

Larger naturally identifiable granularities include:

- Basic blocks - A basic block is a set of instructions which always runs sequentially from beginning to end (Parsons, 1992). There are no branch instructions in the middle of a basic block, and no branch instruction branches into the middle of a basic block. The live inputs of a basic block may include the current state of the registers/flags, and several memory locations.

- Function/procedure calls - A function or procedure call is a jump that passes control to a subroutine (Parsons, 1992). After the subroutine has finished execution, control is returned to the caller. The live inputs of a function call are usually its parameters. The live outputs of a function call are its returned value, and the results of any side-effects it may have.

- Arbitrary sections of code - These are often referred to as *traces*. A trace is a sequence of several instructions which are executed sequentially. A trace may span several basic blocks. A trace ends either when an unconditional branch is made, after a certain number of conditional branches, or after a certain number of instruction executions (Luk *et al.*, 2005).

### 1.2 Why use Value Profiling?

Value Profiling can be used to determine the invariance of the inputs and outputs of over the set of all computations<sup>1</sup> throughout the execution of a program. Invariance in the inputs of a computation is termed *Value Reuse*. The computations with the most Value Reuse can be the target of optimisations to increase the overall performance of the program. Additionally, the profile information can be used to guide these optimisations. Computations with high degrees of Value Reuse may be modified to exploit this behaviour.

Examples of the application of Value Profiling and Value Reuse Optimisations include:

- (Feller, 1998) used Value Profiling to determine the invariance of instructions and their operands, and the values stored in memory locations referenced by load instructions. The Value Profile

---

<sup>1</sup>Recall that a computation could be an individual instruction, a basic block, a function call, or an arbitrary code section.

information was used to guide source-code optimisations of two of the programs profiled, *m88ksim* and *hydro2d*. The modifications led to a speedup of 13% and 12% respectively.

- (Yang & Gupta, 2002) used Value Profile information to show that throughout the execution of a set of 15 benchmarks, up to 48% of memory locations were occupied by 8 benchmark specific distinct values. This information was used to guide the design of an encoding for a low power data bus (Yang *et al.*, 2004).

- (Kumar, 2003) used Value Profiling to determine the invariance of calls to functions in a math library. The Value Profile information was used to guide the implementation of a *Function Evaluation History Table* (FEHT) which stored the results of the most recent calls to the function. The implementation of the FEHT decreased the execution time of the benchmarks tested by up to 6%.

- (Huang & Lilja, 2003) developed a compiler-assisted scheme for reusing the outputs of computations with a granularity between that of instructions and basic blocks, termed *subblocks*. It was shown that a speedup of 36% is possible by reusing the outputs of subblocks chosen by the compiler.

### 1.3 The Low-Level Virtual Machine Compiler Infrastructure

*Low-Level Virtual Machine* (LLVM) is a compilation framework created with the goal of allowing transformation and analysis of arbitrary programs at all stages of compilation and execution (Lattner & Adve, 2004a). The source code to all of the elements of LLVM is available.

Modified versions of GCC (*llvm-gcc*) and C++ (*llvm-g++*) which output LLVM *bitcode* (code compiled to LLVM and stored in its native format) have been created. Any C or C++ program to which the full source code is available can be compiled to LLVM bitcode. Generally no modifications need to be made to the source code - however, some Makefiles may require editing.

LLVM uses a common low-level code representation, called an *Intermediate Representation* (IR). Code compiled by *llvm-gcc* and *llvm-g++* is converted to the LLVM IR. Optionally, an optimisation phase can be run on the generated IR. The LLVM compiler (*llc*) converts the IR to machine code of the required target machine. Several backends are available for the LLVM compiler, including x86, MIPS, PowerPC etc. The same IR is used as the source to generate the machine code for all of the backends.

An interpreter for the LLVM IR bitcode is provided. The organisation of the interpreter source code is quite convenient for instrumentation with additional code to record value profile information. At the IR stage, the target code is in a machine-independent representation. Any profile data gathered using the bitcode interpreter should therefore have relevance for all architectures.

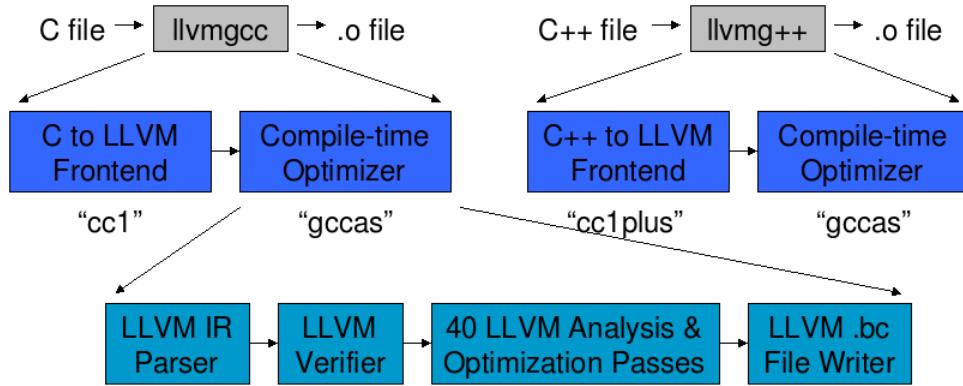

Figure 1.1: The stages of the LLVM compilation process from C and C++.

The above figure, from (Lattner & Adve, 2004b), gives an outline of the stages involved in compiling and optimising a program using LLVM. The C- and C++-to-LLVM frontends output code in LLVM IR. Normally, the LLVM IR will be optimised in the "40 LLVM Analysis & Optimisation Passes" stage, although this is optional. The final output from the "LLVM .bc File Writer" stage can be loaded and executed by the interpreter. The LLVM Compiler, *llc* can be used to compile this .bc file to native code for any supported target, including x86, ARM, etc.

## 1.4 Pin

*Pin* is a tool for the instrumentation of native code (Luk *et al.*, 2005). Architectures currently supported by Pin include the Intel Itanium & IA-32, and the ARM family of processors. An API is provided which allows the development of instrumentation tools. This API abstracts away the details of the target architecture, allowing the developer to focus on the development of tools without having to be aware of the intricacies of the underlying system.

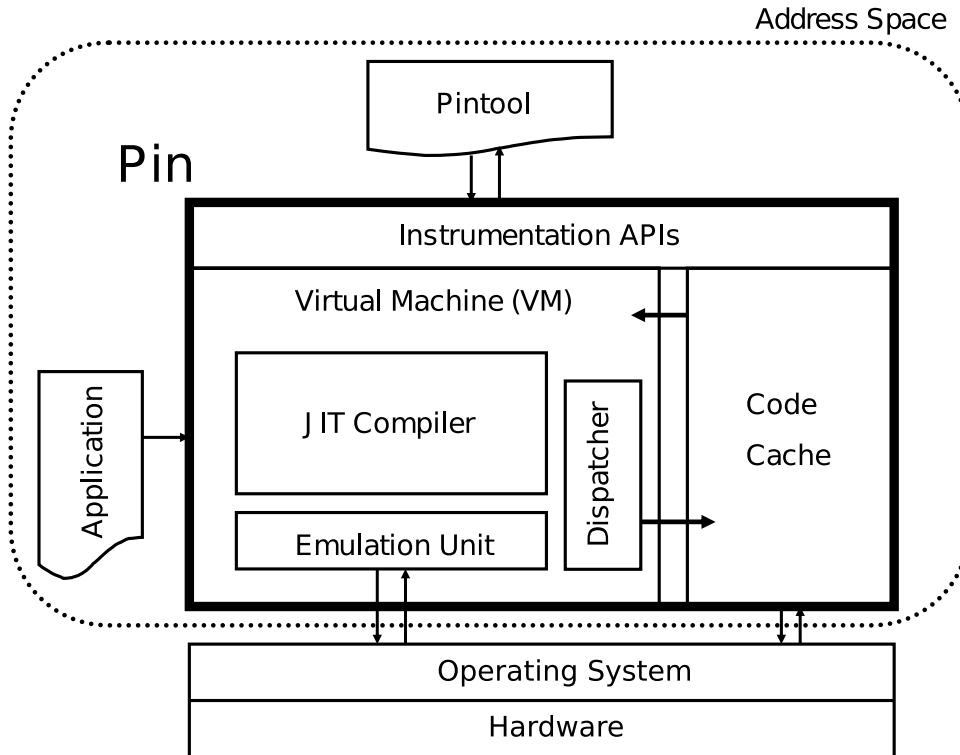

Figure 1.2: The architecture of Pin.

Figure 1.2 from (Luk *et al.*, 2005), shows the architecture of Pin. The programs with which executables are instrumented are called *PinTools*. When Pin is run, the target application and the PinTool are both loaded by Pin. The JIT Compiler recompiles portions of the program to include the instrumentation code and places them in the Code Cache prior to their execution. Additionally, the instrumented portions of code are modified so that when their execution completes, control is returned to the Virtual Machine, which can determine the next portion of code to be executed. If this portion of code has already been recompiled, then it is retrieved from the Code Cache and execution continues. Otherwise, the JIT Compiler is called to recompile and instrument the required portion of code.

In normal operation of an executable (without Pin), the components shown in Figure 1.2 would be reduced to three components: the Application, the Operating System, and the Hardware. The Application would run directly on top of the Operating System layer, which in turn runs on the Hardware layer.

The Pin API is ideal for the development of Value Profiling tools for the x86 architecture. Arbitrary code may be inserted into specific points in the program (e.g. when a memory access takes place, or upon the execution of specific instructions) which can record information about the state of the program. Information about the state of the program for Value Profiling would include the values of instruction operands, or the value being transferred across the memory bus.

## 1.5 MiBench Benchmarks/MiDataSets

The MiBench (Guthaus *et al.*, 2001) set of benchmarks were created with the goal of characterising the workload of embedded processors and microcontrollers. Five categories of benchmarks make up the suite: Industrial control, Network, Security, Consumer Devices, Office Automation and Telecommunications.

Each of the benchmarks are available as C source code. As a result, it is possible to use llvm-gcc to compile each of the benchmarks to the LLVM IR.

Only two input sets are provided with each of the benchmarks, *Small* and *Large*. The Small input set is designed to represent a simple application of the benchmark. The Large input set is designed to represent a more complex, real-world application of the benchmark.

It is expected that performance variations will be exhibited across different input sets for the same benchmark. Therefore, only two input sets are not sufficient to represent a realistic subset of all inputs. MiDatasets (Fursin *et al.*, 2007) provides an additional 18 input sets for each benchmark. Using 20 datasets for each benchmark allows a more representative sample of the performance variations to be generated. Furthermore, the effects of any optimisations can be tested more thoroughly.

## 1.6 Conclusion to Introduction

This project involves the investigation of Value Profiling on LLVM and the x86 architecture (using Pin). Value Profile data is gathered for the MiBench benchmarks in conjunction with the MiDatasets sets of data. This Value Profile data is analysed and used to guide the design of optimisations which exploit Value Reuse. In order to determine a starting point for investigations into Value Profiling, a literature review was undertaken to assess work already complete in this area, and identify areas requiring further investigation.

The structure of this report is as follows: In Chapter 2 a literature review is presented. Chapter 3 outlines areas of investigation and describes how they will be investigated. Chapter 4 describes the implementation of the Value Profiling tools. In Chapter 5 the results of using these tools are presented and analysed. In Chapter 6 a cache which exploits Value Reuse is presented. In Chapter 7, Value Profiling in conjunction with a cache simulator, and an encoding for a low-power data bus is presented. Chapter 8 gives conclusions to the areas of investigation specified in Chapter 3. Chapters 9 and 10 contain an evaluation of the project and further work to be undertaken.

# Chapter 2

## Literature Review

### 2.1 Introduction

The goals of this literature review are to:

- Establish the current state of investigation into Value Profiling.

- Critically assess the work done by others in this area.

- Determine a starting point for investigations into Value Profiling.

- Review the current applications of Value Profiling.

Relevant literature has been gathered and examined. Methods which have been used by others to investigate Value Profiling will be adapted for use with the LLVM infrastructure and Pin in subsequent sections of this report.

### 2.2 Value Profiling

(Calder *et al.*, 1997)

This motivation for this paper is that variables which exhibit invariant or semi-invariant behaviour at run time cannot be easily identified by a compiler. As the compiler cannot identify these variables, or the values they may frequently store, it is not possible to make optimisations to efficiently exploit this behaviour. A method (*Value Profiling*) is proposed and analysed to determine the variables that exhibit semi-invariant behaviour, in order to enable the compiler to make more effective optimisations. Several potential applications of Value Profiling are suggested, including guiding compiler optimisations and providing hints for value prediction hardware.

A software implementation of a Value Profiler is presented. The Value Profiler does not store all the values encountered during the execution of the program - a limited number is stored in a table, and an algorithm is designed to store only the most frequently occurring values. The algorithm maintains a count of how frequently each instruction has been encountered in the last time period. Periodically the table is sorted in descending order of the most frequently executed instructions, and the bottom half of the table (the least frequently encountered half) is cleared to make room for new entries.

An additional Value Profiling scheme is also presented, called *Convergent Value Profiling*. This scheme is designed to reduce the total time taken to produce an accurate Value Profile for a program. At the beginning of the execution, the Value Profiler is set to profile all instruction executions. Throughout the execution of the program, the Value Profiler checks to see if the Value Profile information for each instruction opcode is converging to a steady state. If it is considered that the Value Profile data for a particular opcode has converged, then Value Profiling for that instruction opcode is turned off. As Value Profiling is turned off for each instruction opcode, the speed of the execution of the program will increase as the Value Profiler consumes less time recording Value Profile data. In order to ensure that the Value Profile data is representative of the entire execution of the program, profiling is periodically turned back

on for each instruction opcode. This allows the profiler to determine if the Value Profile for each opcode has moved from its converged state to an unconverged state.

The conclusion to this paper states that the analysis possible with Value Profiling can be used to determine regions of a program which are optimisable. However, schemes to exploit this potential are not presented in this paper.

## 2.3 Dynamic Instruction Reuse

(Sodani & Sohi, 1997)

This paper presents a method for reusing the outputs of instructions which have previously been executed using similar inputs. The paper claims to present the very first implementation of a scheme to reuse the results of previous instruction executions. The motivation for developing this method was originally to reduce the branch misprediction penalty in superscalar architectures. However, it is suggested that other scenarios where instructions with the same inputs and outputs are computed also arise frequently.

A microarchitectural mechanism to reuse the result from a previous computation is described, and is termed a *Reuse Buffer*. The Reuse Buffer stores particular attributes of an instruction, and its output. When an instruction is dispatched, the existence of a similar instruction in the Reuse Buffer is checked. If the instruction already exists in the Reuse Buffer, the stored output is retrieved to avoid re-executing the same instruction.

Three different methods of storing the attributes of an instruction in the buffer are discussed. All of these schemes use the program counter as an index into the Reuse Buffer. Each scheme uses a different method to compare the current instruction with instructions in the Reuse Buffer:

**Scheme 1** stores the operand values of instructions in the Reuse Buffer. The operand values of the current instruction are compared to the operand values of instructions in the buffer which have a program counter entry similar to the address of the current instruction.

**Scheme 2** stores the register names of instructions in the Reuse Buffer. Additionally, this scheme has to keep track of whether results in the reuse buffer are still valid, as data written to registers which an instruction refers to will invalidate the result stored in the reuse buffer. This scheme was devised to make comparison of instructions simple.

**Scheme 3** is a more complicated scheme which establishes chains of dependent instructions, and attempts to track the reuse status of these chains of instructions.

Twelve benchmarks were used to test the effects of each implementation of the reuse buffer. Each scheme was tested with a 32-entry, 128-entry and 1024-entry Reuse Buffer. The Reuse Buffer was implemented as a fully associative buffer. The percentage of reused instructions from each group of instructions was recorded. This instruction profile was used to estimate the speed increase compared to a similar architecture which does not implement a Reuse Buffer.

Scheme 1 reused the most instructions. Scheme 2 performed quite poorly. Scheme 3 performed well, but was still not as effective as scheme 1. Scheme 1 therefore provided the greatest speed increase. A summary graph of the proportions of reused executions from each group of instructions is also given. Integer operations were the most reused<sup>2</sup>, followed by address calculation instructions, and finally control instructions. A 4-way set associative buffer was also implemented, using scheme 1 for instruction comparison. Almost identical performance can be seen between the fully associative and 4-way set associative Reuse Buffers.

The conclusion to the paper states (as this is the original implementation of a value reuse buffer) that there is further work to be done to refine the implementation of reuse buffers, as these preliminary results appear promising. A highlighted area in which further work is to be done is the implementation of a scheme to decide which instructions should be placed into the reuse buffer, as it is observed that around 80% of entries placed in the Reuse Buffer are evicted without ever being reused.

---

<sup>2</sup>These two statements (see overleaf) appear to contradict each other. However, it is possible that there are many integer operations present in floating-point benchmarks, which are responsible for some of the Value Reuse/Value Locality present

## 2.4 An Analysis of the Potential for Global Level Value Reuse in the SPEC95 and SPEC2000 Benchmarks

(Yi & Lilja, 2001)

The contribution of this technical report is to demonstrate the difference between *Local-level Value Locality*<sup>3</sup> (reoccurrence of the same instruction opcode, operands and program counter) and *Global-level Value Locality* (reoccurrence of instruction opcode and operands, but disregarding the program counter). It is suggested that the exploitation of Global-level Value Locality had previously not been investigated as current Value Reuse techniques use the program counter as an index into the Value Reuse Cache.

A method to test whether there is a difference in the amount of Value Locality at the local and global levels is described. Most results are presented as several tables of numbers - though interpretation of the data is not impossible, it is difficult to verify the statements made regarding the results by inspection. The opcodes of instructions which occur frequently in each benchmark are stated. It is stated that there is no significant difference in the level of Value Locality between integer and floating-point benchmarks<sup>2</sup>. It can be seen that every benchmark frequently executes arithmetic instructions, though no conclusions are drawn regarding the distribution of instruction opcodes.

The authors conclude that the results of the experimentation show that there is greater Value Locality at the global level than there is at the local level. It is not explicitly stated whether further investigation into the exploitation of Global-level Value Locality is worthwhile. It is suggested that a large reduction in execution latency for certain instructions (those requiring many cycles to execute) could be made with the implementation of a Value Reuse scheme. However, because there is greater Value Locality at the global level than at the local level, it can be concluded that further investigation into the exploitation of Global-level Value Locality is warranted.

## 2.5 Frequent Value Locality and its Applications

(Yang & Gupta, 2002)

It is shown that for 15 SPEC95 benchmarks, a small number of distinct values are stored repeatedly in main memory. Up to 48% of memory locations were occupied by eight benchmark specific distinct values. The contribution of this paper is to demonstrate applications exploiting the Value Locality of the memory. Applications presented are a low power data bus, and a low power Frequent Value Cache. Both of these applications are relevant in the context of embedded architectures.

The investigation into Value Locality is introduced in the context of existing research by (Lipasti *et al.*, 1996) and (Gabbay & Mendelson, 1997). Three methods of analysing the Value Locality of the benchmarks are presented:

- Frequent Value Occurrence in Memory: A method for determining the top 8 most frequently occurring values in memory is described. The results show that on average, 48% of all memory locations are occupied by eight benchmark specific distinct values. It is shown that of these values, the most frequently occurring value is usually 0.

- Frequent Value Distribution in Time: A method to measure the occurrence of frequent values in memory at regular intervals throughout the execution of the benchmark is presented. Results for this benchmark are presented as plots showing the occurrence of frequent values against time. The authors conclude that it can be seen that the most frequently occurring values occur throughout the entire execution of each of the benchmarks. This conclusion is easily verified by inspection of the plots.

- Frequent Value Distribution in Memory: A method to determine the uniformity (or otherwise) of the distribution of frequent values in memory is described. Results are presented in the form of plots of the frequency of occurrence against memory address. The authors state that frequent values occur with a high degree of uniformity throughout the memory. Therefore, no matter what part of memory is currently in use, frequent values are likely to be observed. This conclusion may also be verified by inspection of the plots.

---

<sup>3</sup>Some literature refers to *Value Locality*. This is synonymous with Value Reuse in this report.

As it has been shown that there is a high degree of Value Locality in memory, the authors hypothesise that frequent values will occur at other areas in the memory hierarchy, including the data bus and the processor cache. The authors propose to test the hypothesis with 15 SPEC95 benchmarks.

Three methods were developed to test this hypothesis:

**Method 1:** The most frequent values in a given program are found once throughout its execution. The program is instrumented to intercept the data values in all load and store operations. When a load or store operation is executed, the value is recorded. If there are multiple occurrences of a value throughout the lifetime of the program, a count of the occurrences is recorded along with the value, rather than storing multiple copies of the same value. At the end of the execution, the list of values is sorted to find the most frequently occurring values.

Results are presented for this method show the percentage of all memory accesses comprised by the top value up to the top 128 values. It can be seen from the graph that in some cases, only one value represents over 70% of all load/store operations. On average, 50% of all accesses are represented by the top 128 values.

Subsequently the benchmarks were re-executed with a different input. The sets of most frequent values found with the first input set were shown to have a large intersection with the most frequent values found using the second input set.

**Method 2:** As Method 1 is not suitable for implementation in hardware, this method was designed as a hardware scheme to find frequent values. A technique similar to the Value Profiling technique presented in (Calder *et al.*, 1997) is used, with a modification. Instead of the lower half of the frequent value table being cleared periodically, a *swapping* mechanism is implemented to sort the table.

This method is shown to be very effective in finding frequent values. A comparison is made for each of the 15 benchmarks between the percentage of frequent value accesses found by the swapping method, and the percentage found by the original value profiling method. Again, a high percentage of frequent value accesses are found. Graphs are presented which show the percentage of frequent value accesses, against the number of instructions profiled. As more instructions are profiled, the percentage of frequent value accesses increases up to a peak percentage. Most benchmarks display between 30% and 50% of memory accesses involving frequent values. Some benchmarks have a much higher percentage, including *m88ksim* at 92%, *su2cor* at 75% and *fpppp* at 78%.

**Method 3:** This method finds a constantly changing set of frequent values throughout the execution of a program. A 32 entry table of frequent values was maintained with a *Least Recently Used* (LRU) eviction policy. On average, 32% of memory accesses involved frequent values found using this method. However, up to 68% of all memory accesses for the *compress* benchmark involved frequent values. The previous two methods had not been as successful in finding frequent values for the *compress* benchmark. This leads the authors to conclude that a changing set of values may provide better results for some benchmarks, though a fixed set of frequent values is successful with others.

As it has been shown that a small number of constantly changing values are frequently involved in memory accesses for all benchmarks, two applications exploiting this characteristic are presented.

**Frequent Value Cache:** A design for a low-power data cache is presented. The cache exploits the Value Locality of memory accesses, by storing the frequent values in an encoded form. The encoded form only requires  $\log_2 n$  bits to represent a frequent value. The set of frequent values do not change throughout the program execution. Some detail of the design is presented, which is omitted from this review.

A simulation was used to estimate the power reduction of the Frequent Value Cache. For a 64KB cache, the power reduction was found to be 33%.

**Frequent Value Encoding:** An encoding was designed for a low-power data bus. Similar to the Frequent Value Cache, the Frequent Value Encoding exploits the Value Locality of memory accesses. Unlike the Frequent Value Cache, the encoding scheme maintains a changing set of 32 frequent

values. A description of the function of the encoding is not be presented here. The results presented show that there is an average of 30% reduction in switching activity on the data bus as a result of the Frequent Value Encoding, thus power consumption is reduced as it is proportional to the switching activity.

In conclusion, this paper has presented a study to determine the prevalence of a small number of frequent values in memory. It has been thoroughly demonstrated that a high percentage of memory locations are occupied by a small number of distinct values. From this, the hypothesis that frequent values will be found elsewhere in the memory hierarchy was formed. This was thoroughly shown to be the case. The two applications developed as a result of these findings are effective in reducing the power consumption of a processor cache and data bus.

An encoding for a low power data bus and a low power Frequent Value Cache are both of relevance to embedded architecture, as many embedded devices operate on battery power, such as mobile phones and PDAs. An investigation into the Value Locality of memory locations is warranted by the results found in this paper. If similar results can be produced, it can be shown that typical applications executed on embedded processors (of which the MiBench suite is representative) may be suitable for hardware schemes to reduce power consumption.

## 2.6 Increasing Instruction-Level Parallelism with Instruction Precomputation

(Yi *et al.*, 2002)

In this paper, a *Precomputation Table* is presented. A Precomputation Table is a small cache on the processor which stores instruction opcodes, operands and the output of the instruction. When a dynamic instruction which has the same opcode and operands as an entry in the Precomputation Table enters the pipeline, the output is retrieved from the Precomputation Table. This output is then stored in the location where the output of the dynamic instruction would have been stored. The instruction is then removed from the pipeline. This process has effectively bypassed execution of the instruction.

15 different SPEC95 and SPEC2000 benchmarks are profiled to determine the top 2048 arithmetic unique computations. Only two different input sets, labelled Input Set A and Input Set B are used for each benchmark. It is shown that between 13.7% and 44.8% of all dynamic instruction executions are due to the top 2048 arithmetic unique computations.

The top arithmetic unique computations from the Input Set A are then used to populate a Precomputation Table in the simulated hardware that the benchmarks are executed on. Each benchmark is re-executed using Input Set A, with varying sizes of Precomputation Table. The execution of each benchmark is profiled to determine which instructions were bypassed, and this information is used to speculate on the percentage speedup as a result of using the Precomputation Table. Table sizes used were 16, 32, 64, 128, 256, 512, 1024 and 2048. The percentage speedup for each benchmark and Precomputation Table size is presented in a graph, which is convenient for interpretation of the results. It can be seen that in general, larger sizes of Precomputation Table increase the percentage speedup. The percentage speedup is between 4.6% and 12.2%, depending on the size of the Precomputation Table, and the benchmark being executed. Each benchmark is then re-executed and profiled with Input Set B, still using the Precomputation Table from Input Set A. The percentage speedup for each of the benchmarks for Input Set B is slightly lower than that of Input Set A for each size of Precomputation Table.

The authors conclude that this shows that the input set does not determine which are the most frequently executed arithmetic unique computations, but rather this this is a characteristic of the benchmark. Whilst the results do not disagree with this conclusion, more input sets could have been tested to verify this conclusion. There is no discussion of how similar the two input sets were. It may be possible to choose two input sets which have greatly differing sets of most frequently occurring unique arithmetic computations.

A comparison is made between the percentage of speedup gained by using a Precomputation Table and the percentage speedup gained by using an implementation of a Value Reuse Cache. Precomputation Tables with 32, 256 and 2048 entries are compared against Value Reuse Caches with 32, 256 and 2048 entries. Details of how the Value Reuse Cache is implemented are not given. It would have been useful if

the eviction policy of the Value Reuse Cache were documented, as this would aid in making comparisons of the results and conclusions in this paper with those in other papers.

The Precomputation Table is loaded with the precomputations from Input Set A. The benchmarks are executed with Input Set B. It is likely that this is done to compare the worst-case speedup of instruction precomputation with value reuse rather than the best case. The results show that there is a greater percentage speedup obtained by using a precomputation table than by using an equivalent size Value Reuse Cache in almost all cases.

The authors conclude that the benefits of Instruction Precomputation exceed the benefits of Value Reuse, and do so with less hardware complexity. This claim cannot be verified without more information on the implementation of the Value Reuse Cache. However, it is expected that a Value Reuse Cache requires more complex hardware. As the value reuse table is dynamic, extra hardware would be required to manage its contents.

## 2.7 Value Reuse Optimization: Reuse of Evaluated Math Library Function Calls Through Compiler Generated Cache

(Kumar, 2003)

This paper presents a compiler scheme for reusing the results of function calls made to the math library. The compiler instruments a program with code which implements a cache of the results of function calls. The instrumented code performs a lookup in the cache to determine if the result has previously been computed, to avoid redundant calls to the function. This cache is called the *Function Evaluation History Table* (FEHT).

Kumar states that it is important to consider the difference in the execution times of the instrumented and original versions of the program. This is to avoid the case where the instrumented program takes longer to execute than the original one. The method for managing the contents of the FEHT must be carefully determined. Three potentially viable methods are presented.

The first, round robin, is a simple algorithm which replaces entries in the FEHT using a variable to denote the index of the entry to be replaced. Each time a new entry is to be added, the current entry is replaced with the new entry, and the counter which keeps track of the current entry is incremented by one. If the call placed within a loop, the induction variable of the loop is used as the index to the entry to be replaced.

The second scheme is based on profiling the program to determine which inputs to the math library function occur most frequently. The results of these most frequent calls are then hard-coded into the instrumented program. The modified program performs a lookup in the set of precomputed results to determine if it already has the result of a function call. If it does not have a precomputed result, the function has to be called to compute the result.

Kumar's final scheme is based on a combination of the first two - a lookup table is included for precomputed frequent values, and a round-robin buffer is implemented.

It is stated that the scheme is not unilaterally applied to all math library function calls, as this would almost certainly slow down the execution of the program. A heuristic based on the probability of a high frequency of calls to the math library at a particular call site is used to determine which function calls to instrument.

The effect of the compiler scheme was tested using seven benchmarks. The number of call sites instrumented and the FEHT size for each function are listed in a table. It can be seen that only a small number of call sites (between 1 and 12) are instrumented. The FEHT size is also very small, set at 1 entry for all benchmarks except *alvinn*, which has an FEHT size of 10.

The results presented show that execution time is decreased in most cases by a small percentage - the results are presented in a very small graph so it is difficult to determine exact values. However, it is stated that the maximum decrease in execution time is 6%. Another graph shows that the reduction in the number of calls to the math library is quite dramatic - up to 99% in some cases. However, it seems logical that this does not translate to an increase in speed of 99%, as the program must now spend time searching through and managing the FEHT.