IMPERIAL COLLEGE LONDON

DEPARTMENT OF COMPUTING

# **Generatively Programming Galerkin Projections on General Purpose Graphics Processing Units**

By

Graham Markall

Supervisor: Prof. Paul Kelly

Second Marker: Dr. Tony Field

Submitted in partial fulfilment of the requirements for the MSc Degree in Advanced Computing

of Imperial College London

September 2009

## Abstract

This report presents the results of a preliminary investigation into using abstract specifications of finite element methods to generate code that performs the assembly of a system of linear equations on multicore architectures, with a focus on NVidia's CUDA language. This investigation has been conducted with the goal of integrating generated code into Fluidity, a general-purpose computational fluid dynamics code. We survey and evaluate CUDA implementations of finite element assembly, in particular examining the optimisations necessary for high performance, and examine the state of the art in the automatic generation of finite element assembly code.

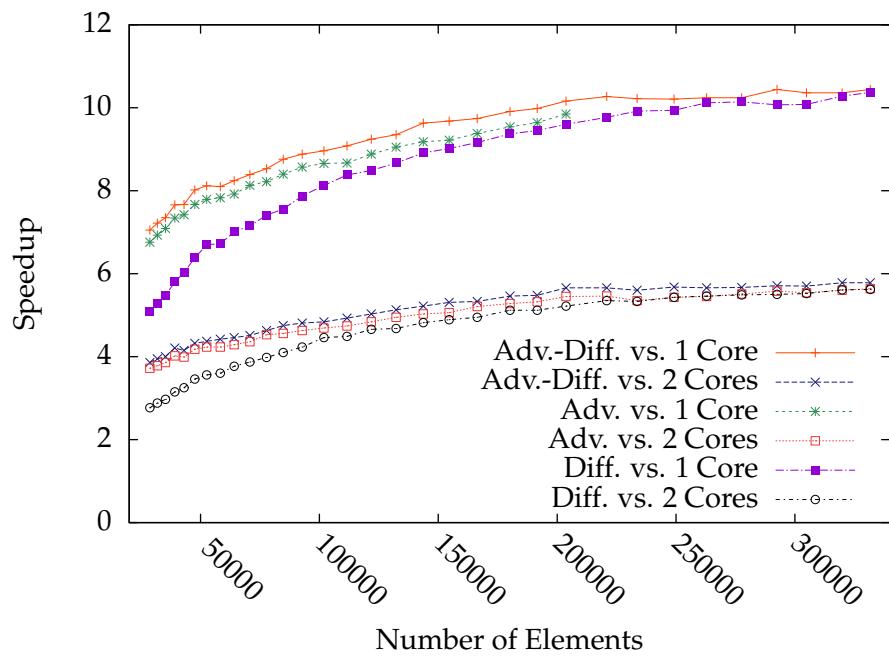

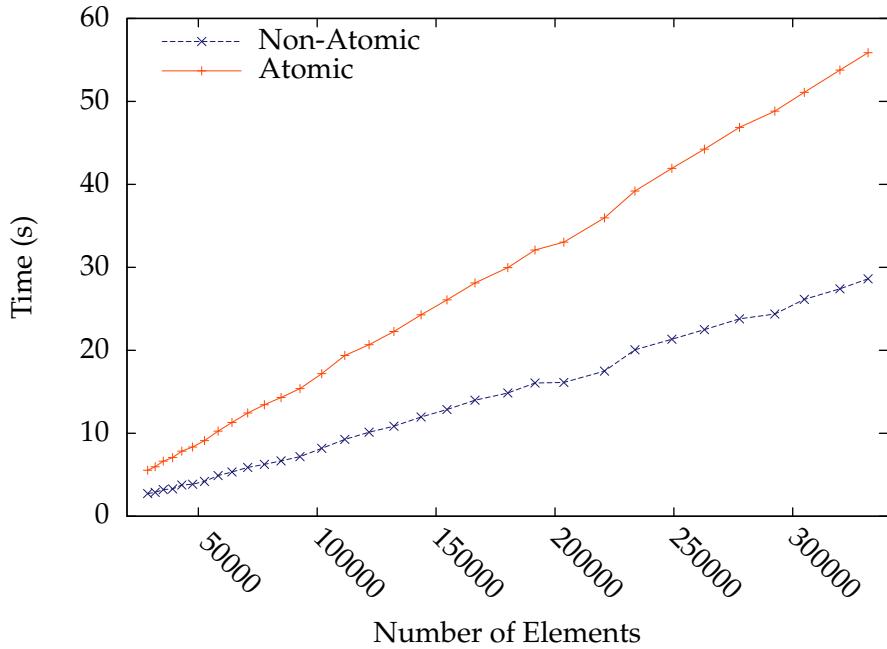

CUDA implementations of the assembly phase of Fluidity test programs that solve Poisson's Equation and an Advection-Diffusion equation are presented. We demonstrate a performance improvement of almost an order of magnitude over a multicore CPU implementation for the Advection-Diffusion equation on typical hardware performing computations using double-precision arithmetic. We identify that the performance of the CUDA implementation is limited by the use of atomic operations, and the use of the Compressed Sparse Row matrix format, both of which are costly. We outline how further significant performance gains may be achieved by modifying our implementation to overcome these limitations.

These implementations are used to guide the design of a prototype compiler, which we use to demonstrate the feasibility of generating CUDA code from abstract specifications. We outline further work based on the research we have conducted, with a long-term goal of converting the low-level Fortran implementations of finite element assembly in Fluidity into high-level abstract specifications, to facilitate the exploitation of future multicore architectures.

## Acknowledgements

People who I would like to thank for their contributions to the success of this project are:

- Paul Kelly, who has dedicated a large number of hours to the supervision of this project. His guidance, support, and helpful suggestions throughout the duration of this project have been invaluable. I would also like to express gratitude for the support he gave me throughout the first ISO, and general advice throughout the duration of the MAC course.

- David Ham, for many things, including: spending a large amount of time explaining the finite element method and the Fluidity codebase; for writing the test problem without which I would not have been able to demonstrate success in this project; for making time to answer all my questions and read drafts of my report; for his guidance and encouragement; and for making this project a possibility.

- Anton Lohmotov, for spending a great deal of time examining drafts of my report and providing lots of helpful suggestions and comments.

- Francis Russell, for many interesting discussions, and for prompting me to think about how iteration might be captured in UFL.

- Lee Howes, Gerard Gorman and Patrick Farrell for their advice and suggestions regarding the performance results, and for interesting discussions.

# Contents

|          |                                                                                                    |           |

|----------|----------------------------------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                                                                | <b>1</b>  |

| 1.1      | Project Outline . . . . .                                                                          | 1         |

| 1.2      | Contributions . . . . .                                                                            | 2         |

| 1.3      | Presentation . . . . .                                                                             | 2         |

| <b>2</b> | <b>Background</b>                                                                                  | <b>3</b>  |

| 2.1      | Introduction . . . . .                                                                             | 3         |

| 2.2      | The NVidia Tesla GPU Architecture and CUDA Programming Language . . . . .                          | 3         |

| 2.2.1    | The Parallel Programming Model . . . . .                                                           | 5         |

| 2.2.2    | The Memory Hierarchy . . . . .                                                                     | 5         |

| 2.2.3    | Introducing CUDA . . . . .                                                                         | 7         |

| 2.2.4    | Remarks . . . . .                                                                                  | 7         |

| 2.2.5    | Other Multicore Architectures and Languages . . . . .                                              | 8         |

| 2.3      | The Finite Element Method . . . . .                                                                | 8         |

| 2.3.1    | Discretising the Domain . . . . .                                                                  | 9         |

| 2.3.2    | Assembly and Solution . . . . .                                                                    | 9         |

| 2.3.3    | Boundary Conditions . . . . .                                                                      | 10        |

| 2.4      | Fluidity . . . . .                                                                                 | 11        |

| 2.4.1    | <code>test_laplacian</code> . . . . .                                                              | 11        |

| 2.4.2    | <code>test_advection_diffusion</code> . . . . .                                                    | 12        |

| 2.5      | The Unified Form Language . . . . .                                                                | 13        |

| 2.5.1    | UFL Compiler Optimisations . . . . .                                                               | 14        |

| 2.6      | Summary . . . . .                                                                                  | 14        |

| <b>3</b> | <b>Related Work</b>                                                                                | <b>17</b> |

| 3.1      | Introduction . . . . .                                                                             | 17        |

| 3.2      | Finite Element Assembly on GPUs . . . . .                                                          | 17        |

| 3.2.1    | The Genesis of the Finite Element Method on Graphics Processors . . . . .                          | 17        |

| 3.2.2    | Hyperelastic Material Simulation . . . . .                                                         | 17        |

| 3.2.3    | Discontinuous Galerkin on GPUs . . . . .                                                           | 19        |

| 3.2.4    | Soft Tissue Modelling in the SOFA Framework . . . . .                                              | 21        |

| 3.2.5    | High-Order Earthquake Modelling . . . . .                                                          | 23        |

| 3.2.6    | Finite Element in CPU/GPU Clusters . . . . .                                                       | 23        |

| 3.3      | Generating Execution Schedules for Tensor Contractions . . . . .                                   | 23        |

| 3.4      | Pycuda . . . . .                                                                                   | 24        |

| 3.5      | Generative Programming/Automation of Finite Element Methods . . . . .                              | 25        |

| 3.5.1    | Remarks . . . . .                                                                                  | 25        |

| 3.6      | Conclusions . . . . .                                                                              | 26        |

| <b>4</b> | <b>Implementation of Finite Element Assembly using CUDA</b>                                        | <b>29</b> |

| 4.1      | Introduction . . . . .                                                                             | 29        |

| 4.2      | Initial Implementation of the assembly routine of <code>test_laplacian</code> using CUDA . . . . . | 29        |

| 4.2.1    | The Assembly Loop in Fortran . . . . .                                                             | 29        |

|          |                                                                                                    |           |

|----------|----------------------------------------------------------------------------------------------------|-----------|

| 4.2.2    | Implementation of Boundary Conditions . . . . .                                                    | 31        |

| 4.2.3    | Translation Methodology . . . . .                                                                  | 31        |

| 4.2.4    | Integration with a GPU Conjugate Gradient Solver . . . . .                                         | 33        |

| 4.2.5    | Testing . . . . .                                                                                  | 33        |

| 4.2.6    | Initial Performance Results . . . . .                                                              | 34        |

| 4.2.7    | Optimising Kernels . . . . .                                                                       | 34        |

| 4.2.8    | Ensuring Coalesced Memory Accesses . . . . .                                                       | 36        |

| 4.2.9    | Post-Optimisation Performance . . . . .                                                            | 37        |

| 4.3      | Implementation of the Assembly Phase of <code>test_advection_diffusion</code> Using CUDA . . . . . | 37        |

| 4.3.1    | Kernels Used in this Implementation . . . . .                                                      | 39        |

| 4.3.2    | Testing . . . . .                                                                                  | 40        |

| 4.4      | Performance Results and Analysis . . . . .                                                         | 43        |

| 4.4.1    | Performance of the Assembly Phase . . . . .                                                        | 43        |

| 4.4.2    | Speedup and Throughput . . . . .                                                                   | 43        |

| 4.4.3    | Overall GPU Performance . . . . .                                                                  | 45        |

| 4.4.4    | Performance Improvement . . . . .                                                                  | 49        |

| 4.5      | Conclusions . . . . .                                                                              | 52        |

| <b>5</b> | <b>A UFL Compiler for CUDA</b> . . . . .                                                           | <b>53</b> |

| 5.1      | Introduction . . . . .                                                                             | 53        |

| 5.2      | Design . . . . .                                                                                   | 53        |

| 5.2.1    | The Backend . . . . .                                                                              | 53        |

| 5.2.2    | A UFL Frontend . . . . .                                                                           | 54        |

| 5.2.3    | Integration With Fluidity . . . . .                                                                | 57        |

| 5.3      | Implementation . . . . .                                                                           | 57        |

| 5.3.1    | The Python Frontend . . . . .                                                                      | 57        |

| 5.3.2    | The Code Generation Backend . . . . .                                                              | 58        |

| 5.4      | Testing . . . . .                                                                                  | 59        |

| 5.4.1    | Generation of Test Input for the Backend . . . . .                                                 | 59        |

| 5.4.2    | Generation of Test Input for the Frontend . . . . .                                                | 60        |

| 5.4.3    | Generation of Further Inputs . . . . .                                                             | 60        |

| 5.5      | Conclusion . . . . .                                                                               | 61        |

| <b>6</b> | <b>Evaluation</b> . . . . .                                                                        | <b>63</b> |

| 6.1      | Introduction . . . . .                                                                             | 63        |

| 6.2      | Examination of the Implementations of the Assembly Phase . . . . .                                 | 63        |

| 6.3      | Discussion of the UFL Compiler . . . . .                                                           | 64        |

| 6.4      | Examination of UFL . . . . .                                                                       | 65        |

| 6.5      | Summary . . . . .                                                                                  | 66        |

| <b>7</b> | <b>Conclusions and Future Work</b> . . . . .                                                       | <b>67</b> |

| 7.1      | Conclusions . . . . .                                                                              | 67        |

| 7.2      | Further Work . . . . .                                                                             | 67        |

| 7.2.1    | Performance Optimisation of the GPU Implementations . . . . .                                      | 67        |

| 7.2.2    | Completion of Support for UFL . . . . .                                                            | 67        |

| 7.2.3    | Implementation of Additional Backends . . . . .                                                    | 68        |

| 7.2.4    | Generation of GPU Kernels . . . . .                                                                | 68        |

| 7.2.5    | Automated Exploration of Optimisations . . . . .                                                   | 68        |

| 7.2.6    | Development of Interface Code . . . . .                                                            | 68        |

| 7.2.7    | Capture of Iteration in UFL . . . . .                                                              | 68        |

| 7.3      | Manifesto . . . . .                                                                                | 68        |

| <b>A</b> | <b>Optimised Kernel Library</b> . . . . .                                                          | <b>69</b> |

|                                                |           |

|------------------------------------------------|-----------|

| <b>B UFL Codes for Advection and Diffusion</b> | <b>71</b> |

| B.1 Advection . . . . .                        | 71        |

| B.2 Diffusion . . . . .                        | 71        |

# Chapter 1

## Introduction

*Fluidity* [Gorman *et al.*, 2008] is a general-purpose computational fluid dynamics package developed by the Applied Modelling and Computation Group in the Department of Earth Science and Engineering at Imperial College. Explorations into using NVidia *Graphics Processing Units* (GPUs) to accelerate iterative solvers in Fluidity have been performed [Markall and Kelly, 2009, Perryman and Kelly, 2008] with results showing an order of magnitude speedup on typical hardware. However, iterative solvers are a generic part of many computational science programs, and a large research effort is devoted to using GPU hardware for their acceleration [Buatois *et al.*, 2007, Bolz *et al.*, 2005, Wiggers *et al.*, 2007, Cevahir *et al.*, 2009, Wang *et al.*, 2009]. For these reasons, it is thought to be more profitable to focus our efforts on accelerating the Assembly phase, which is specific to Fluidity.

There are several issues with using GPUs to accelerate applications. Doing so requires extensive modification of existing code. This prohibits their use for accelerating many applications, as making such modifications requires a large amount of effort. Often there is a large investment in an existing codebase, and making these modifications requires that large portions of it are obsoleted. Also, although the CUDA language [NVidia, 2007] and the NVidia Tesla Architecture [Lindholm *et al.*, 2008] are presently dominant, this will change in the future. Further extensive modifications must be made to an application each time a new architecture is targeted.

### 1.1 Project Outline

This project is an investigation into how Fluidity may be modified to exploit current and emerging multicore architectures by providing a hardware-independent abstraction for the specification of numerical methods, in particular the finite element method [Sherwin *et al.*, 2009]. Methods described using this abstraction will be compiled by a source-to-source translator which rewrites the abstract specification as a concrete implementation for the target architecture. This separation of the specification of numerical methods and their low-level implementation provides two key advantages:

- Methods specified in this language are “future-proofed”: since the specification provides no description of the low-level implementation, re-targeting to future architectures only requires the development of a new code-generation backend.

- The development of numerical methods is eased: programming numerical methods is often tedious and error prone, requiring much code that is not directly related to implementing a new method, but is necessary in order to support its execution. Since a high-level specification prescribes the numerical method purely in terms of mathematical operations, the burden of writing low-level code is removed from the programmer. Mathematicians may rapidly prototype new numerical methods, and programmers are free to concentrate on other aspects of the software.

In this project we have focused on the NVidia Tesla architecture [Lindholm *et al.*, 2008] only. The work completed as part of this investigation divides into two stages:

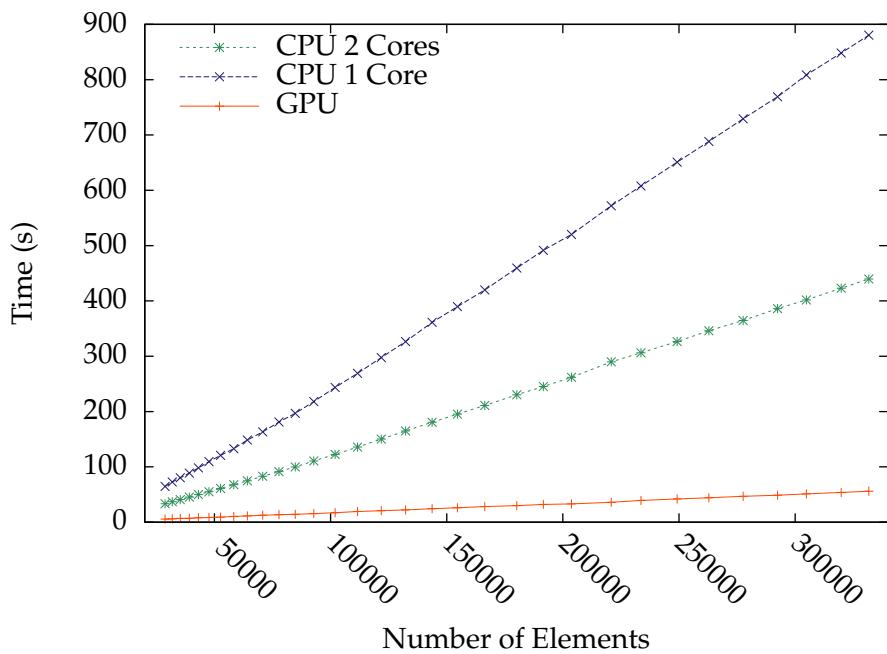

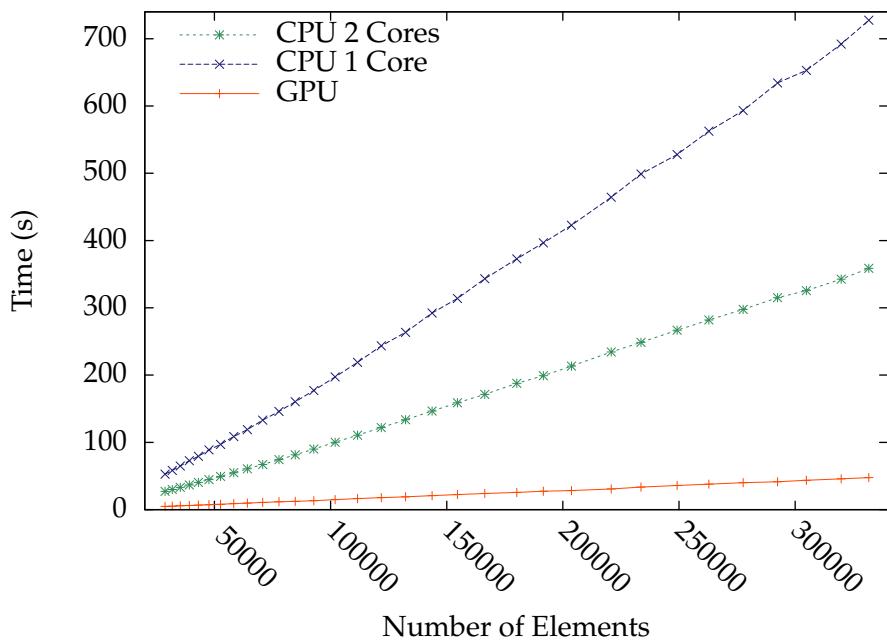

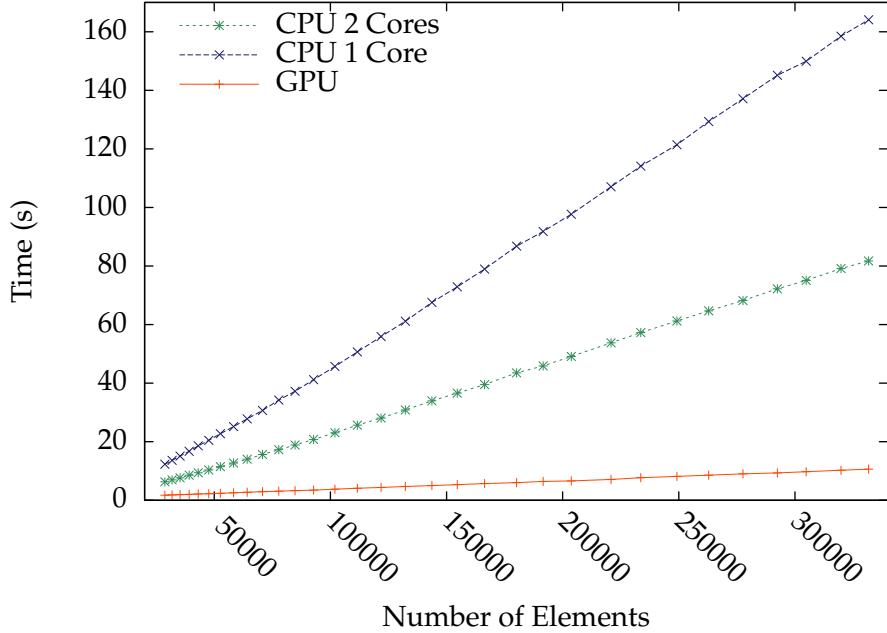

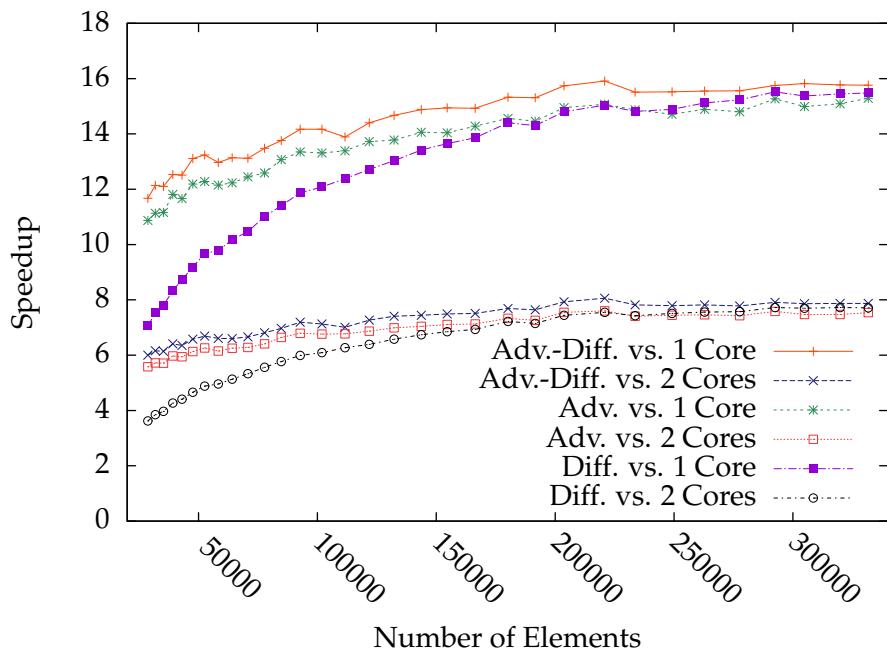

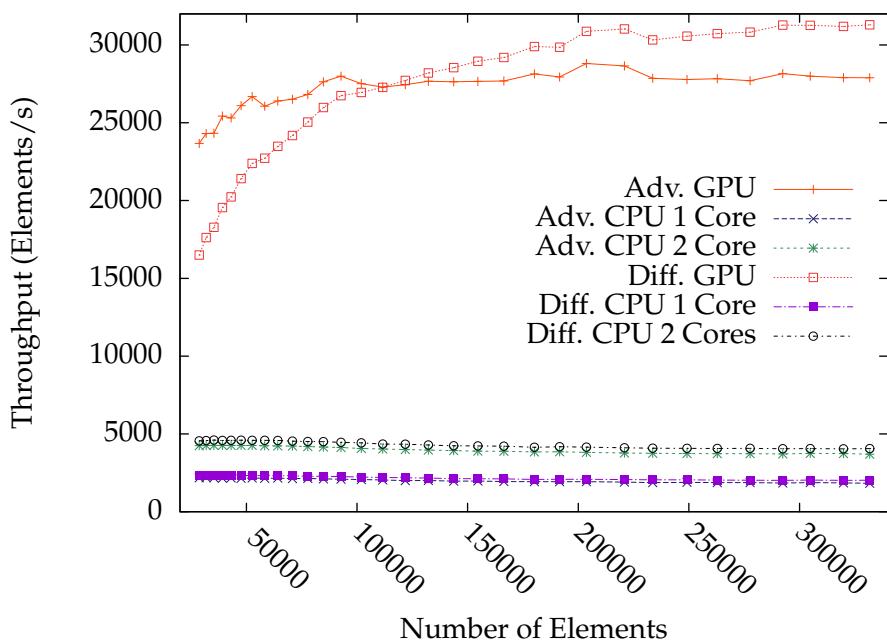

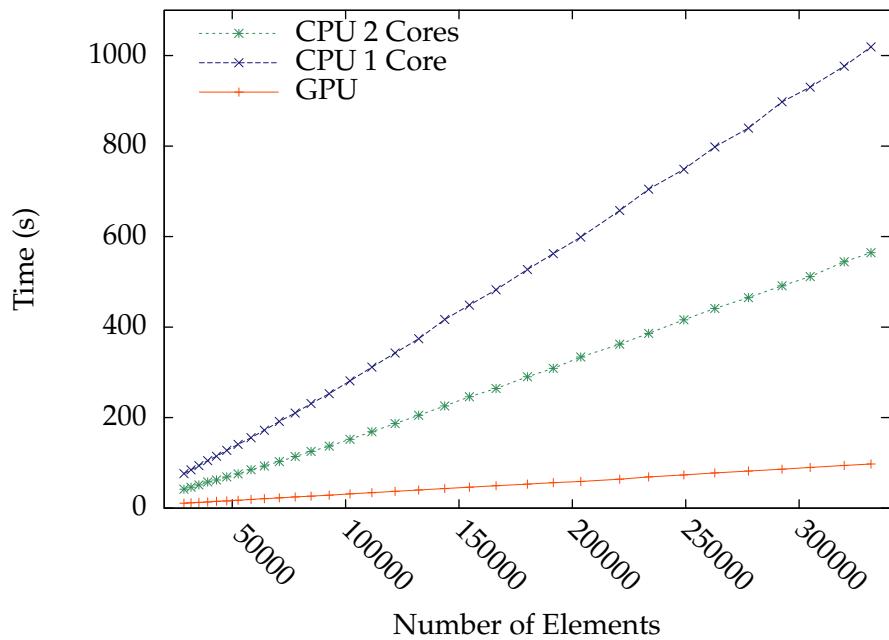

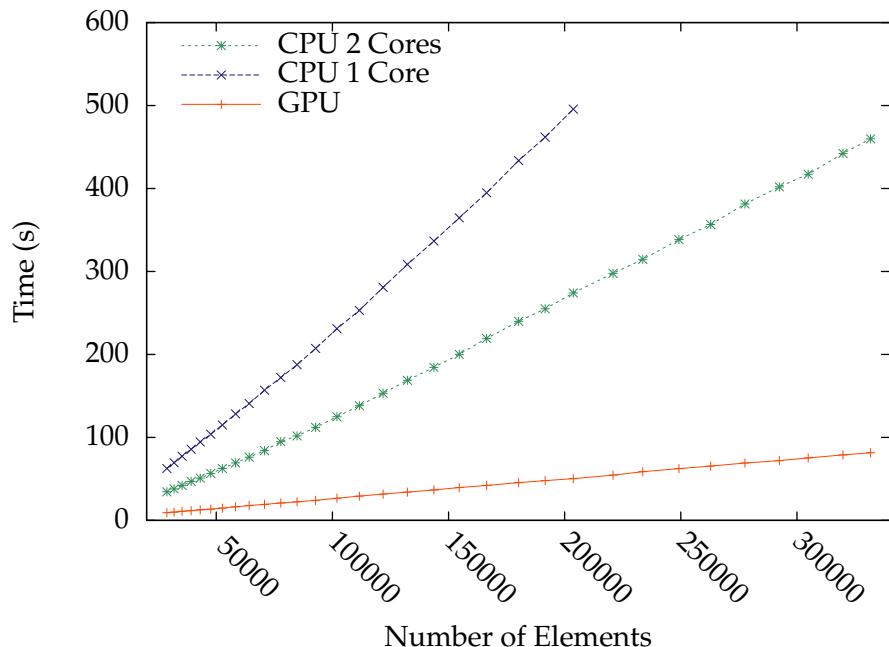

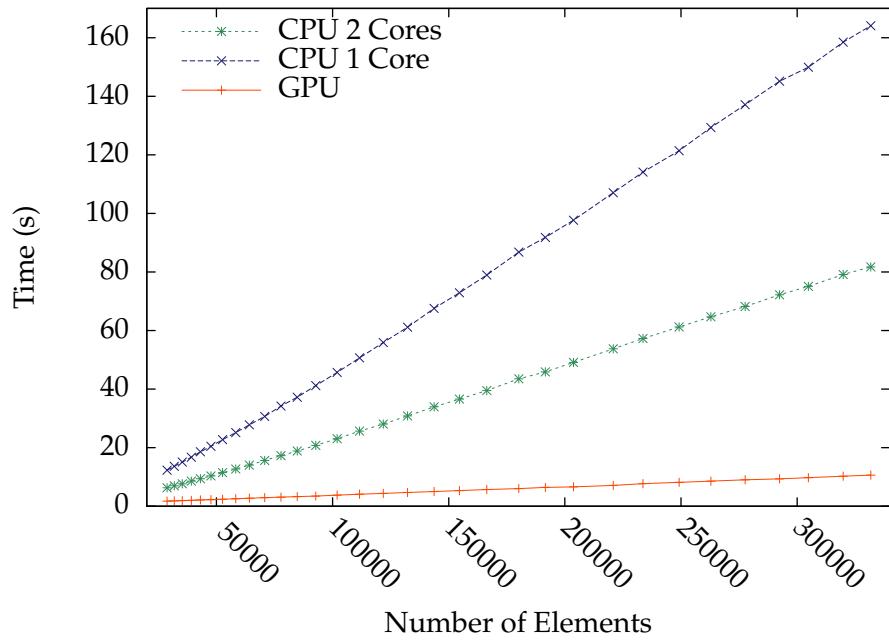

1. GPU Implementations of the assembly phase for two Fluidity test programs were produced (Chapter 4). These implementations provide proof that substantial performance improvements may be obtained using GPUs for finite element assembly (Section 4.4), and form the basis of experiments to determine how further improvements may be obtained (Section 4.4.4).

2. An implementation of a prototype compiler that generates target-specific output code from a high-level specification has been developed (Chapter 5). This prototype demonstrates the feasibility of generating code for different target architectures from a single high-level specification.

## 1.2 Contributions

- We survey existing approaches to the automatic generation of finite element assembly code and evaluate them (Section 3.5). We also survey and evaluate the state of the art in GPU acceleration of finite element assembly (Section 3.2).

- We describe the implementation of a library of kernels that perform common operations in finite element assembly on the NVidia Tesla architecture. We present and evaluate strategies that have been used to optimise the performance of this library (Chapter 4).

- We show how this library is used to implement the finite element assembly phase for a variety of test problems, resulting in performance improvements of almost an order of magnitude over the equivalent CPU implementation on typical hardware (Chapter 4).

- We present a prototype implementation of a compiler which compiles descriptions of a finite element assembly phase (written in the *Unified Form Language* [Alnaes and Logg, 2009b]) into CUDA code which uses the kernel library previously described. We describe how the compiler converts the abstract, declarative specification of UFL into an imperative form that is used to generate CUDA code (Chapter 5).

- We evaluate the implementation of the UFL Compiler and show that this prototype demonstrates that the construction of a fully-fledged UFL compiler that supports multiple backends and optimisations is feasible and worthwhile (Section 6.3).

- We examine the Unified Form Language and show that it provides a sound platform for further research in this area due to the level of abstraction that it provides (Section 6.4).

## 1.3 Presentation

The research conducted throughout this project has been presented at the 8th International Workshop on Unstructured Mesh Numerical Modelling of Coastal, Shelf and Ocean Flows, under the title *Fitting the Ocean onto a graphics card: towards running ICOM on massively parallel processors* [Markall *et al.*, 2009].

# Chapter 2

## Background

### 2.1 Introduction

In this chapter we introduce the background material and concepts upon which our work is built. We begin by introducing the NVidia Tesla architecture, and the CUDA programming language used to develop software for this architecture. Subsequently, we provide a brief description of the finite element method, and define the Galerkin Projection. We go on to introduce Fluidity, and give an overview of the test problems, which we focus on throughout the remainder of the report. Finally, we discuss the Unified Form Language.

### 2.2 The NVidia Tesla GPU Architecture and CUDA Programming Language

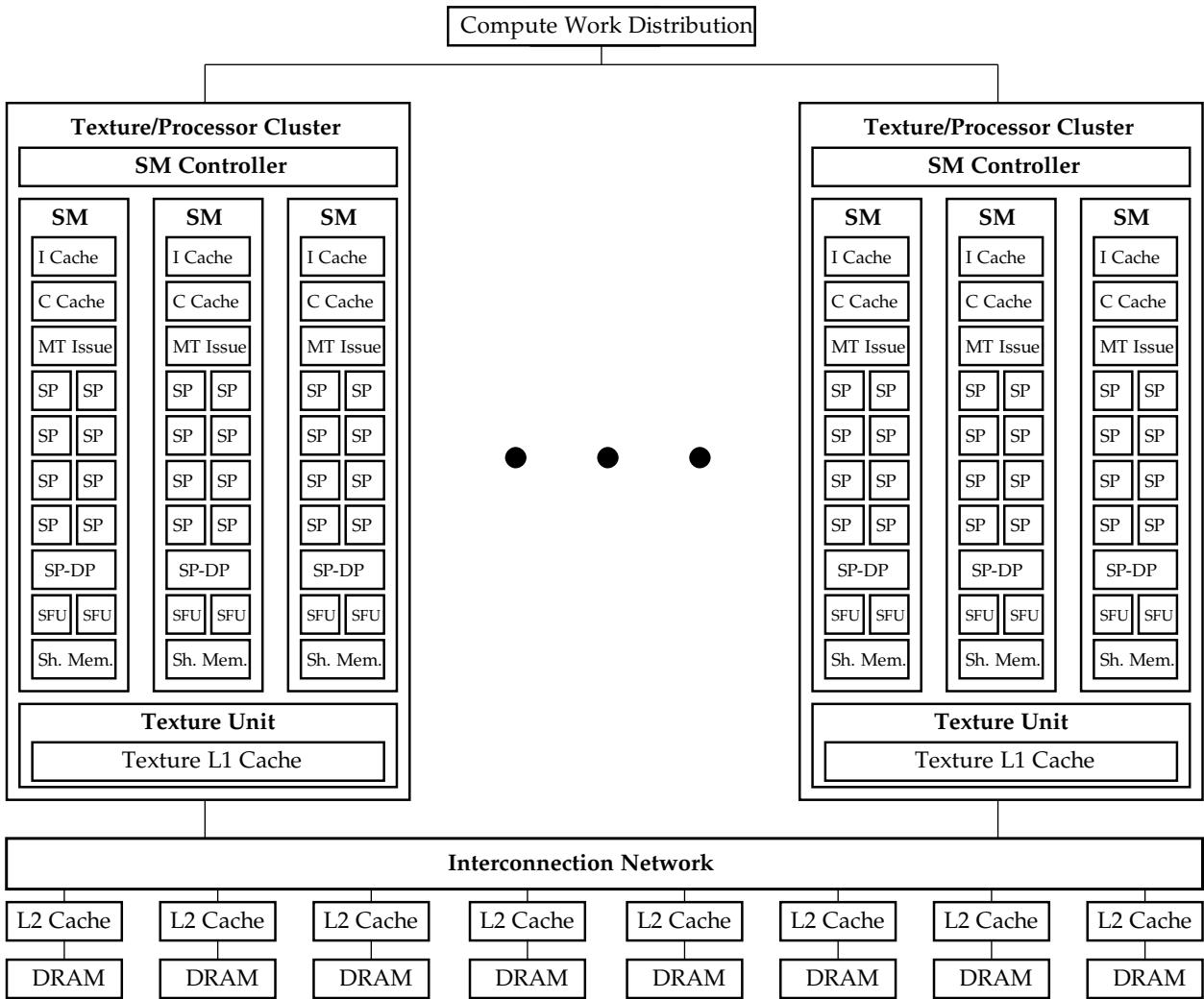

The NVidia Tesla Architecture is a highly-parallel architecture made up of many minimally complex processing elements which are specialised to perform arithmetic operations. In this report we consider the most recent architecture, the GT200 architecture. Figure 2.1 shows an overview of its design.

The GT200 has 10 *Texture/Processor Clusters* (TPCs), which each consist of three *Streaming Multiprocessors* (SMs). Each SM contains various components. The operation of each component in an SM is as follows:

**Compute Work Distribution.** When a kernel is launched, this unit schedules individual units of work (blocks) onto each SM.

**Streaming Processor.** Each SP is a pipelined processor which executes instructions on scalar operands. Each SM has eight SPs that can perform integer or single-precision floating point arithmetic, and one SP which can perform computations on double-precision floating-point operands. The streaming processors also share a register file, consisting of 16384 registers, supporting the execution of a large number of threads on each SM.

**Multithreaded Issue.** The MT Issue unit issues instructions to each of the SPs. Since there is only one MT Issue unit, each SP in an SM must execute the same instruction concurrently.

**Special Function Units.** These units are specialised processors which perform mathematical operations such as sine and cosine. We do not make use of the SFUs in this work, and do not consider them further.

**Caches.** Each SM has an instruction cache, which is similar to the instruction cache of a typical processor. The constant cache stores data that does not change throughout the execution of a kernel.

Figure 2.1: NVidia GTX280 Architecture, as in [Lindholm *et al.*, 2008]. Eight of the identical Texture/Processor clusters are omitted. SM: Streaming Multiprocessor. SP: Streaming Processor. SP-DP: Streaming Processor (Double Precision). I/C Cache: Instruction and Constant Caches. MT Issue: Multithreaded Issue.

**Shared Memory.** The Shared Memory is a software-controlled cache. It may be used by a programmer to store temporary data that is frequently used throughout a computation, in order to increase performance by reducing accesses to the global (main) memory.

**Texture Unit.** The Texture unit contains a read-only cache. Areas of memory which are bound (by the programmer) to Texture Memory are automatically serviced by this cache.

**Interconnection Network.** The GT200 architecture has eight banks of memory, necessitating an interconnection network to allow each SM to access data in any of the banks.

### 2.2.1 The Parallel Programming Model

To make use of a GPU, the programmer writes small programs called *kernels* which execute on the GPU hardware. These kernels are called by programs running on the CPU in the host machine. The program running on the host is also responsible for transferring data to and from the memory of the GPU.

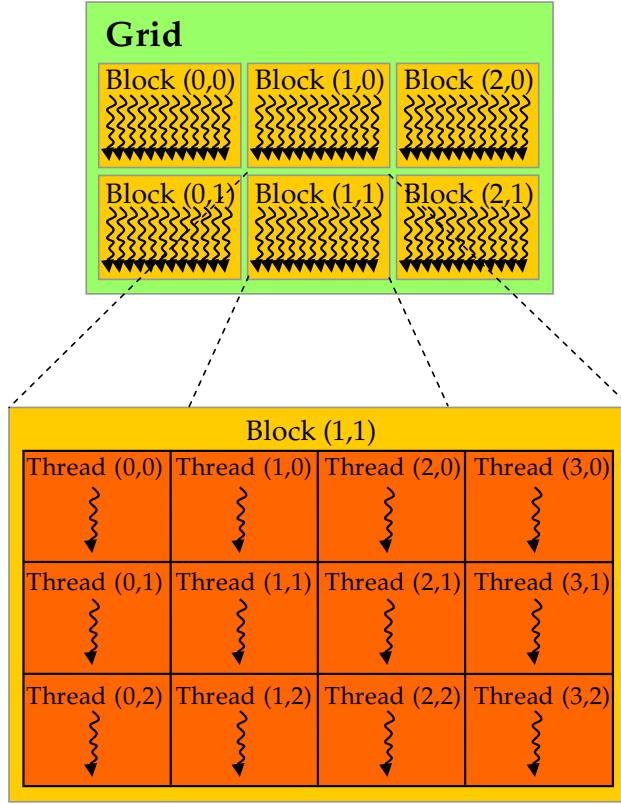

The kernels are programmed using a *Single-Instruction, Multiple-Thread* (SIMT) programming model. This model allows the programmer to divide work (usually data-parallel operations) between a large number of threads. Threads are grouped at several granularities:

**Warps.** A warp is a group of 32 threads that are all within the same block. Threads within a warp all share the same program counter, and as a result must all execute the same instruction concurrently. In the case where threads within a warp diverge in their execution path (for example, when encountering an `if/then/else` construct), the execution of each branch is serialised. It is important to minimise divergence within a warp to obtain maximum performance.

**Blocks.** The next level of granularity is the thread block. Each block is mapped onto a particular SM, and has an affinity to that SM for the lifetime of the kernel. Every thread within a block has its own block-unique identifier (the Thread ID), which may be indexed in one, two, or three dimensions. The choice of the number of dimensions in the index is influenced by the algorithm being implemented. Consider an example of an image filter, which would be likely to be implemented using 2D indexing. This will allow straightforward calculation of the coordinates assigned to a particular thread based on its Thread ID.

**The Grid.** Only one grid exists, which contains all the thread blocks. Each block within the grid has a block-unique identifier, which has one or two dimensions.

A schematic representation of a 2D grid with 2D thread blocks is shown in Figure 2.2. Each thread and block has its unique identifier marked. The organisation of warps in this scenario is omitted from the diagram.

The choice of the number of threads within a block and the number of blocks within the grid are left to the programmer, subject to hardware limitations. Choosing the optimal number of threads per block is aided by use of the CUDA Occupancy Calculator [Nvidia, 2009c], a tool which may be used to estimate the performance of different configurations. In order to ensure that each SM has enough work to do to maximise its utilisation, it is important to use a large number of blocks.

### 2.2.2 The Memory Hierarchy

The memory hierarchy in the Tesla architecture consists of several levels, which serve different purposes. This is in contrast to a more typical architecture, in which successive levels of the hierarchy have larger storage capacities, but increasing access latencies. A description of each level of the hierarchy follows:

**Global Memory.** This is a large area of memory accessible by any thread and the host. Its contents are stored in the DRAM behind the interconnection network. Accesses to Global Memory have a latency of several hundred cycles.

Figure 2.2: A two-dimensional grid of two-dimensional thread blocks. From [NVidia, 2007].

**Registers.** Local variables within kernels are stored in registers where possible. Registers may be accessed within few cycles.

**Local Memory.** The compiler attempts to use registers for the local variables within kernels. When a kernel has too many local variables, some of them are allocated into the DRAM. Although local memory is stored in the same hardware as the global memory, its use is transparent from a programming perspective, and only the thread owning a piece of data in Local Memory may access it. The latency of Local Memory accesses is the same as that of Global Memory accesses.

**Shared Memory.** The Shared Memory may be accessed more quickly than Global and Local Memories, but more slowly than registers. Threads within one block all access the same portion of Shared Memory. Pre-fetching frequently used data into shared memory may improve performance by reducing time spent waiting for accesses to Global Memory.

**Texture Memory.** The programmer may bind areas of data in global memory to Texture Memory. When data is accessed from these areas using a texture fetch, the texture cache is automatically used. This can increase performance for read-only data.

**Constant Cache.** The programmer may pre-load the constant cache with values which do not change throughout the lifetime of a kernel. This may increase performance by reducing the need to go to global memory for these constant values.

**L2 Cache.** The L2 cache is transparent to the programmer. Unlike a traditional L2 cache, it does not provide faster access to data when a hit occurs. Instead, the latency of the L2 cache is not significantly less than that of the DRAM, but overall performance is increased due to reduced pressure on the main memory [Volkov and Demmel, 2008].

### 2.2.3 Introducing CUDA

The CUDA programming language is a set of extensions to the C programming language. These extensions allow a programmer to write kernels which map on to the Tesla architecture. An API is provided that contains functions for initialising the GPU, transferring data between the host machine and the GPU, and for launching kernels.

To give a brief overview of kernels in CUDA, we consider an example. Figure 2.3 shows a naïve implementation of a kernel which computes  $y = \alpha x + y$  for a scalar  $\alpha$  and vectors  $x$  and  $y$ , written in C. The code uses a loop which iterates over each element in the vectors.

```

void daxpy(double a, double *x, double *y, int n) {

for(int i=0; i<n; i++)

y[i] = y[i] + a*x[i];

}

```

Figure 2.3: DAXPY Kernel in C.

To convert this function to a CUDA kernel, the loop is partitioned so that each thread takes on a portion of the work. Since each thread is within exactly one block, we can use the thread and block indices to calculate a unique portion of the vector for the thread to work on, using the `THREAD_ID` macro. This unique index is then used to initialise the induction variable for the loop. Instead of each thread incrementing its induction variable by 1, it is increased by the total number of threads. Figure 2.4 shows the CUDA implementation of a DAXPY kernel. This implementation assumes that the threads and blocks have one-dimensional Thread IDs and Block IDs respectively.

```

#define THREAD_ID (threadIdx.x+blockIdx.x*blockDim.x)

#define THREAD_COUNT (blockDim.x*gridDim.x)

__global__ void daxpy(double a, double *x, double *y, int n) {

for(int i=THREAD_ID; i<n; i+=THREAD_COUNT)

y[i] = y[i] + a*x[i];

}

```

Figure 2.4: DAXPY Kernel in CUDA.

It is clear from this example that getting started with CUDA is a straightforward task for a programmer already familiar with C. There are a minimal number of extra keywords in the language that allow the use of shared memory, synchronisation between threads within a block, data transfer etc., which we omit from this discussion; in-depth documentation of the API is provided in [NVidia, 2009a].

### 2.2.4 Remarks

Although it is very easy to start using CUDA, optimising the performance of CUDA kernels is non-trivial. Often the optimal configuration of thread and block size, and the level of the memory hierarchy to use for items of data are not obvious. To optimise an implementation, a programmer must experiment with various different choices. Debugging kernels is often tricky, with limited tools available for this purpose at present. These factors all contribute to making the optimisation process difficult and error-prone.

In addition, the programmer must write code to explicitly manage the transfer of data to and from the GPU. Making use of shared memory involves additional complexity, as data must be marshalled at the beginning and/or the end of the execution of a kernel. In general, the requirement of writing code to manage the memory hierarchy is a detriment to programmer productivity [Howes *et al.*, 2009b, Howes *et al.*, 2009a].

Since the CUDA programming language is not portable to other architectures, the work invested in optimising a CUDA program might be lost when moving to a new platform. Furthermore, future NVidia hardware may have different performance characteristics to the current generation, so optimised code may have to be re-tuned in the future.

### 2.2.5 Other Multicore Architectures and Languages

There are a number of other multicore architectures available or in development at present, each of which have different programming models and languages. These include the Intel Larrabee [Seiler *et al.*, 2008], the Sony/Toshiba/IBM Cell Processor [Gschwind *et al.*, 2006], and AMD's Stream architecture [Advanced Micro Devices, 2008]. It is clear that another architecture may become dominant in the future, which must be considered when deciding whether to invest in the development and optimisation of codes for the Tesla architecture.

In an attempt to standardise development for multicore architectures, The Khronos Group has developed the OpenCL Specification [Khronos Group, 2008], which describes a language that may be compiled to different multicore platforms. As with CUDA, OpenCL code must be optimised for each different target architecture.

## 2.3 The Finite Element Method

The *Finite Element Method* is a numerical technique for computing the solution to Partial Differential Equations. In this section, we give a brief description of the main steps in the method. A more complete introduction is given in [Sherwin *et al.*, 2009]. We begin with a general linear problem,

$$L(u) = q \quad (2.1)$$

where  $L(u)$  is a linear operator, which in general consists of differential operators ( $\frac{\partial}{\partial X}$ ,  $\frac{\partial^2}{\partial X^2}$ , etc.). The function  $L(u)$  is referred to as the *trial function*. In the exact solution to this equation, the left-hand side is exactly equal to the right-hand side. When using a numerical method, an approximate solution is usually computed, rather than the exact solution. In this approximate solution, the LHS and RHS may not be exactly equal<sup>1</sup>. Denoting the computed solution  $u^\delta$ , we have

$$R(u^\delta) = L(u^\delta) - q \quad (2.2)$$

where  $R(u^\delta)$  is the *residual*, or error in the solution. When the computed solution is exact,  $u^\delta = u$ , and  $R(u^\delta) = 0$ . However, when a numerical approximation is produced, the form of  $R(u^\delta)$  is unknown, so this term must be eliminated. To do this, we multiply the equation by a *test function*,  $v$ , and integrate over the domain  $\Omega$ :

$$\int_{\Omega} vR(u^\delta) dX = \int_{\Omega} vL(u^\delta) dX - \int_{\Omega} vq dX. \quad (2.3)$$

Finally we eliminate the integral of the residual by setting it equal to 0, and are left with

$$\int_{\Omega} vL(u^\delta) dX = \int_{\Omega} vq dX. \quad (2.4)$$

We now have the so-called *weak form* of the linear differential equation in which the definition of equality has been weakened: to satisfy this equation, instead of requiring  $L(u^\delta) = q$ , we only require that both sides are equal after multiplication with an arbitrary function and integration over the domain of the problem.

---

<sup>1</sup>in almost all non-trivial cases, they are not exactly equal.

### 2.3.1 Discretising the Domain

Although we have now relaxed the constraints for a candidate solution, finding an analytical solution to Equation 2.4 will be challenging or impossible. In most cases, we must content ourselves with an approximate numerical solution, evaluated at a finite number of points. However, the form of Equation 2.4 defines the solution to exist within a continuous functional space. Therefore, we need to find a way to convert from this infinite-dimensional, continuous space, to a finite-dimensional discrete space.

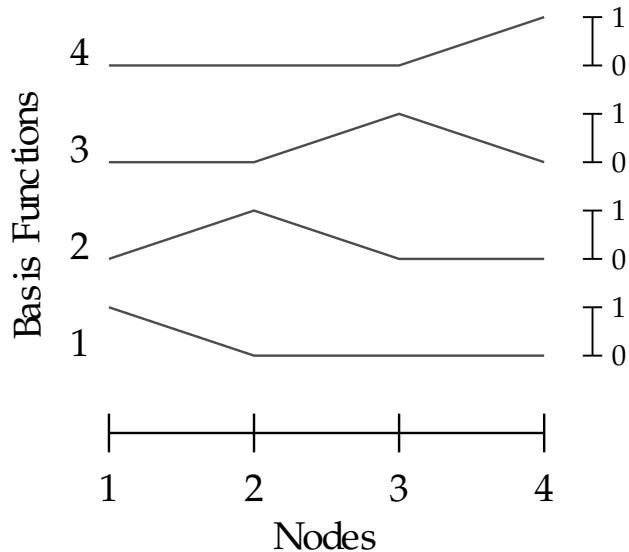

In order to achieve this, we represent the solution  $u^\delta = \sum_{i=0}^{N-1} \hat{u}\Phi_i$  where  $N$  is the number of points in the discrete space, and each  $\Phi_i$  is a basis function of the *trial space*. This gives us a way of approximating the infinite-dimensional trial function as a point in a finite-dimensional space. In Galerkin's method, which we consider in this project, we choose  $v = \sum_{j=0}^{N-1} \hat{v}\Phi_j$ . This choice makes the basis functions of the test function and the trial function the same, and the *test space* is the same space as the *trial space*. The basis functions  $\Phi_i$  are defined such that

$$\Phi_i(x_i) = 1, \text{ and } \forall k : i \neq k, \Phi_i(x_k) = 0 \quad (2.5)$$

where  $x_i$  is the  $i$ -th node in a grid of discrete points in the domain. For example, in a 1D domain we might define the basis functions such that they are piecewise linear as follows:

$$\Phi_i = \begin{cases} \frac{x-x_{k-1}}{x_k-x_{k-1}} & \text{if } x \in [x_{k-1}, x_k] \\ \frac{x_{k+1}-x}{x_{k+1}-x_k} & \text{if } x \in [x_k, x_{k+1}] \\ 0 & \text{otherwise.} \end{cases} \quad (2.6)$$

We may alternatively define basis functions of higher order, provided that they are piecewise continuous and satisfy the condition given in Equation 2.5. Figure 2.5 shows that in a four-node 1D domain, there are four basis functions, as defined in Equation 2.6.

Figure 2.5: Piecewise continuous linear basis functions of order 1 over a four-node, three element one dimensional domain  $\Omega$ .

### 2.3.2 Assembly and Solution

Having discretised the computational domain, we may now go about finding the solution in this discrete domain. This amounts to computing the projection of the solution in the test space onto the trial space. The left-hand side of Equation 2.4 defines an inner product between the test function  $v$  and the trial function  $L(u)$ , which may be considered as a projection of  $v$  into  $L(u)$  (and

vice-versa). This projection is known as the *Galerkin Projection*. In practice, to evaluate this projection, we assemble a system of linear equations

$$Ax = \mathbf{b} \quad (2.7)$$

$\mathbf{b}$  is a known vector of coefficients of the basis functions of the solution in the test space. The known matrix  $A$  defines the projection from the test space to the trial space. Finally, the unknown vector  $\mathbf{x}$  represents the solution in the trial space.

There is a correspondence between the right-hand side of Equation 2.4 and the vector  $\mathbf{b}$ . Since the function  $q$  is known, we may directly evaluate it at any point. In order to discretise the function, we treat it in the same way as the test and trial function spaces, and assume that its numerical approximation is of the form  $q^\delta = \sum_{i=0}^{N-1} \hat{q}_i \Phi_i$ . In the case where  $q$  is constant or linear, it is exactly represented by  $q^\delta$ ; otherwise, the function  $q^\delta$  needs to be approximated such that  $q^\delta = q$  at each mesh point. As a result, the value of  $q^\delta$  is known at each node, and we can use this information to construct the right-hand side vector  $\mathbf{b}$ .

To assemble each row  $A_i$  of the matrix  $A$ , we integrate the left-hand side over each element adjacent to the node  $i$ . This provides a row of  $A$  coupling adjacent nodes. In practice this is achieved by integrating the left-hand side over each element, which produces an  $n \times n$  matrix, called an *element-local matrix* or just *local matrix* where  $n$  is the number of nodes per element. The terms in this matrix are then added into the *global matrix*,  $A$ , at positions dependent upon the node numbers of the element.

The left-hand side often consists of integrals that cannot be efficiently evaluated analytically, so a numerical scheme such as Gaussian quadrature must be used. Since these quadrature schemes evaluate a function over a predefined interval (for example,  $[1, -1]$  in Gaussian quadrature), it is necessary to compute the transformation from this reference interval to the actual physical location of each element. This transformation may be used to approximate the value of the integral over the element in its physical space. For a more complete discussion of how element-local matrices are computed, see [Sherwin *et al.*, 2009].

Having assembled  $A$  and  $\mathbf{b}$ , the system of equations may be solved. In most systems  $A$  is very large and sparse. Since direct solution methods are often impractical for systems of this nature, iterative solvers are preferred. When  $A$  is symmetric and positive-definite, the Conjugate Gradient (CG) method [Shewchuk, 1994] is often the most efficient algorithm for finding a solution. For other systems, the Generalised Minimum Residual (GMRES) method [Barrett *et al.*, 1994] is preferred.

### 2.3.3 Boundary Conditions

Often boundary conditions are a necessary condition for the existence of a unique solution to a differential equation. Boundary conditions may be classified as follows:

**Dirichlet BCs.** Dirichlet BCs specify the exact value of the solution at a particular boundary node.

A crude way to impose a Dirichlet BC at node  $i$  is after the assembly of  $A$ , to zero out all entries of the  $i$ -th row apart from the diagonal entry, which is set to 1, and to set the  $i$ -th element of  $\mathbf{b}$  to the prescribed value. In practice this is inefficient, and many implementations avoid the assembly of entire rows where a Dirichlet BC is applied.

**Neumann BCs.** Neumann BCs specify the value of a derivative at a boundary node. A characteristic of the finite element method is that if no boundary condition is explicitly applied to a boundary node, a Neumann boundary condition  $\frac{\partial u}{\partial X} = 0$  is implicitly applied at that node. The application of Neumann BCs usually involves surface integration over the boundary in question, resulting in a terms which are added into  $\mathbf{b}$ .

**Robin BCs.** Robin BCs are a weighted combination of Neumann and Dirichlet BCs. In practice, they are rarely used.

In order to reduce the complexity of the implementation, the application of boundary conditions has not been included in the software developed throughout this project.

## 2.4 Fluidity

The Fluidity [Gorman *et al.*, 2008] code uses the finite element method to solve a wide variety of systems, including the compressible flow of Newtonian fluids in conservative and non-conservative form on unstructured, adaptive meshes. It may be used for ocean modelling, solving the incompressible non-hydrostatic Boussinesq equations, including additional terms for tidal simulation such as those representing the gravitational interaction of the Earth and Moon, and equilibrium tide and Coriolis terms. As well as supporting the modelling of a wide range of different problems, various finite element discretisations including continuous Galerkin, Petrov-Galerkin, and discontinuous Galerkin are supported, using a variety of element types. For a complete overview of these topics and a description of the code, refer to the Fluidity manual [Ham *et al.*, 2009].

A large effort has been devoted to parallelising Fluidity on distributed architectures using MPI. The code is regularly tested against experimental data and theoretical test cases [Farrell *et al.*, 2009], ensuring the correctness of the solutions it produces. It may be noted that there has a large investment of time, money and effort into the development of the Fluidity codebase.

In order to exploit multicore architectures such as the NVidia Tesla, a large portion of this investment will be obsoleted, and further effort will be required as development, testing, and tuning of CUDA code will be necessary. As stated in Section 2.2.4, the value of this additional investment might be short-lived, as exploitation of emergent multicore architectures will require further iterations of the development cycle. As a result, it is infeasible to port Fluidity to new multicore architectures using the low-level programming languages and tools that are usually provided for this purpose.

In the following two subsections, we describe the equations and their discretisations that are solved in two test programs, `test_laplacian` and `test_advection_diffusion`. We focus on these two problems throughout the rest of this project.

### 2.4.1 `test_laplacian`

The `test_laplacian` program is the most minimal test program in Fluidity. The purpose of the program is to solve the equation

$$\nabla^2 u = f \quad (2.8)$$

over the unit square. The Neumann boundary condition  $\frac{\partial u}{\partial x} = 1$  is applied to one edge of the square. The right-hand side function defined as

$$f(x, y) = \frac{\pi}{4} \left( \cos\left(\frac{\pi}{2}x\right) \cos\left(\frac{\pi}{2}y\right) + \frac{\pi}{2} \sin\left(\frac{\pi}{2}x\right) \right). \quad (2.9)$$

To solve this equation using the finite element method, we multiply by a test function  $v$  and integrate over the domain:

$$\int_{\Omega} v \nabla^2 u \, dX = \int_{\Omega} v f \, dX \quad (2.10)$$

As it is not possible to use a second derivative in a bilinear form we need to integrate the left-hand side term by parts to lower the order of the derivative. This leads to:

$$-\int_{\Omega} \nabla v \cdot \nabla u \, dX + \int_{\partial\Omega} v \nabla u \cdot \mathbf{n} \, ds = \int_{\Omega} v f \, dX \quad (2.11)$$

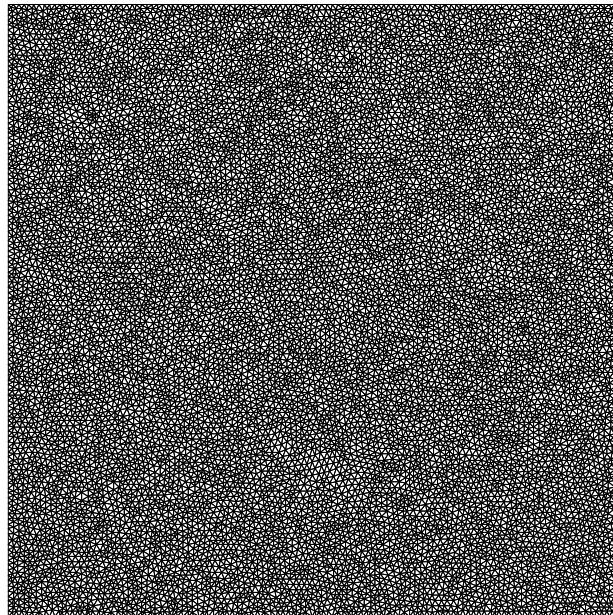

This system may then be discretised, assembled, and solved, to find the value of  $u$  at each point in the discrete domain. In the test program, the basis functions are equivalent to those defined in Equation 2.6.

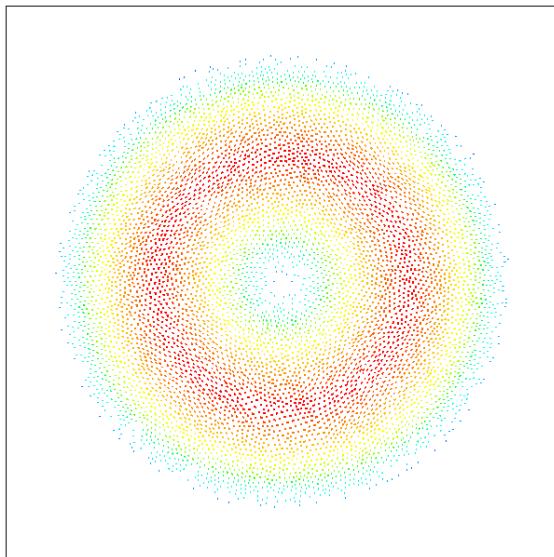

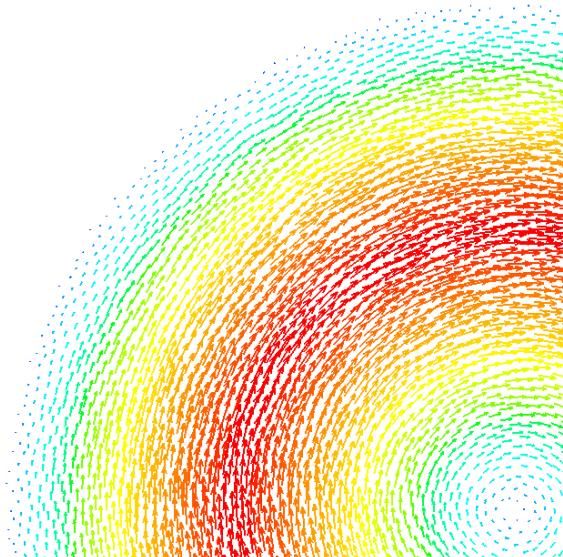

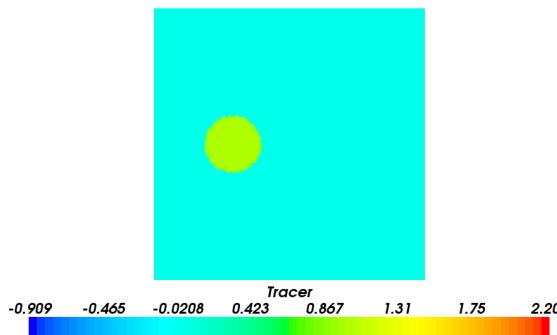

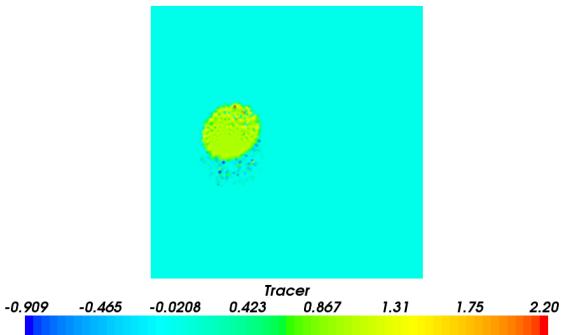

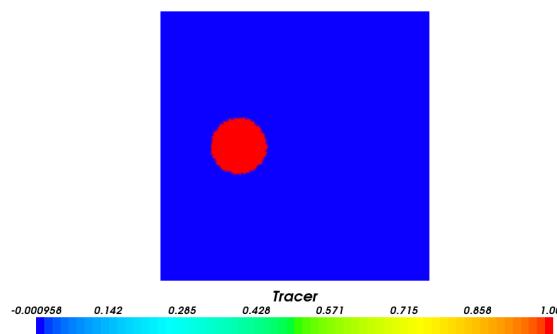

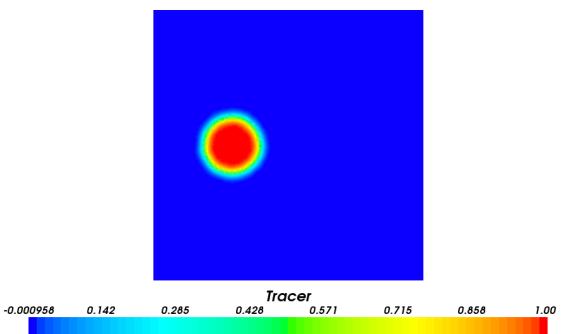

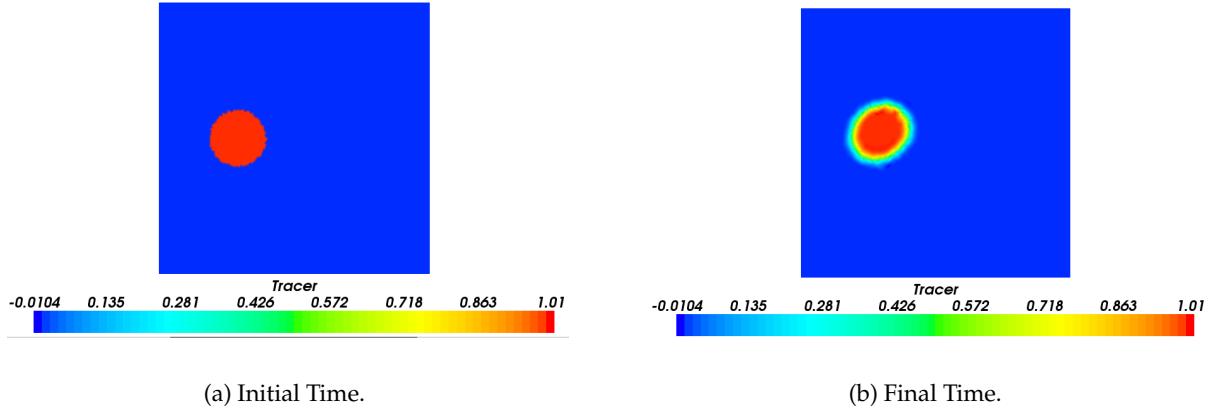

## 2.4.2 test\_advection\_diffusion

This test program has been written by David Ham, a member of the Applied Modelling and Computation Group, for the purpose of comparison with a CUDA implementation. The program determines the concentration of a tracer (such as saline, or dye) throughout the domain at a given time, given an initial tracer concentration, and the velocity and diffusivity throughout the domain. The following description of the method is reproduced from the documentation of this test problem [Ham, 2009b]. The system may be modelled using the advection-diffusion equation:

$$\frac{\partial T}{\partial t} + \nabla \cdot (\mathbf{u}T) = \nabla \cdot \bar{\mu} \cdot \nabla T \quad (2.12)$$

where  $T$  is the tracer concentration,  $\mathbf{u}$  is a vector representing the velocity, and  $\bar{\mu}$  is a rank-2 tensor of diffusivity. We may physically interpret the second left hand side term as one which describes the advection of the tracer, and the right hand side term as describing the diffusion, both with respect to time. Multiplying this equation by a test function  $q$  and integrating over the domain  $\Omega$  with boundary  $\partial\Omega$  gives:

$$\int_{\Omega} q \frac{\partial T}{\partial t} dX + \int_{\Omega} q \nabla \cdot (\mathbf{u}T) dX = \int_{\Omega} q \nabla \cdot \bar{\mu} \cdot \nabla T dX \quad (2.13)$$

Integration of the advection and diffusion terms by parts gives:

$$\int_{\Omega} q \frac{\partial T}{\partial t} dX - \int_{\Omega} \nabla q \cdot \mathbf{u} T dX + \int_{\partial\Omega} q T \mathbf{n} \cdot \mathbf{u} ds = - \int_{\Omega} \nabla q \cdot \bar{\mu} \cdot \nabla T dX + \int_{\partial\Omega} q \mathbf{n} \cdot \bar{\mu} \cdot \nabla T ds \quad (2.14)$$

We fix the boundary condition to

$$\int_{\partial\Omega} q T \mathbf{n} \cdot \mathbf{u} ds - \int_{\partial\Omega} q \mathbf{n} \cdot \bar{\mu} \cdot \nabla T ds = 0 \quad (2.15)$$

which implies that the domain of the simulation is perfectly insulated: no tracer will leave the domain by being advected or diffusing through the walls of the domain. A useful side-effect of this boundary condition is that it is implicitly assembled into the system of equations, simplifying the implementation. Applying this boundary condition to Equation 2.14 gives the following:

$$\int_{\Omega} q \frac{\partial T}{\partial t} dX - \int_{\Omega} \nabla q \cdot \mathbf{u} T dX = - \int_{\Omega} \nabla q \cdot \bar{\mu} \cdot \nabla T dX \quad (2.16)$$

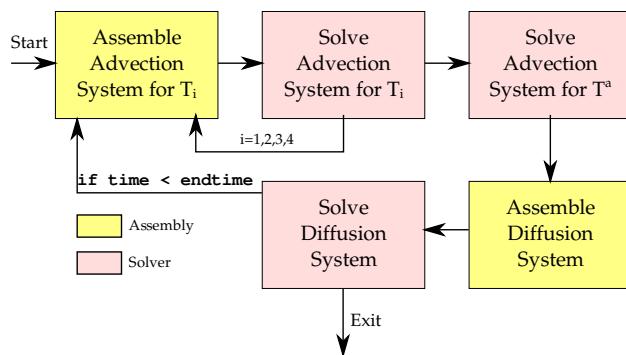

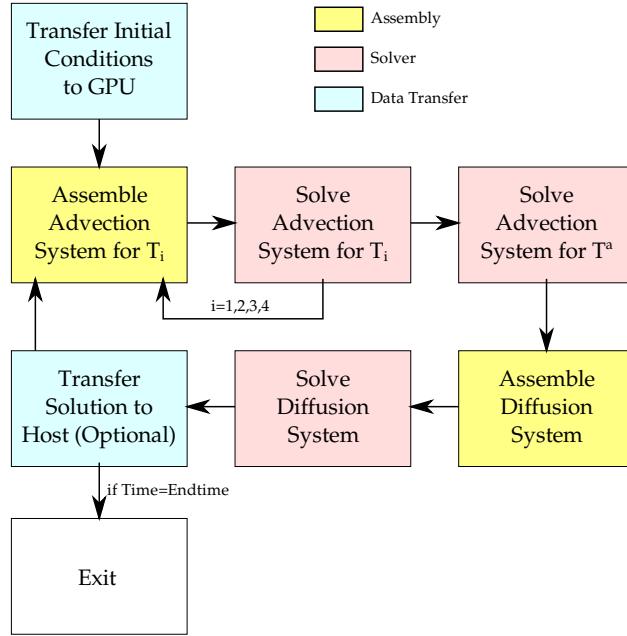

To compute  $T^{n+1}$  (the solution at time  $n+1$ ) given  $T^n$  (the solution at time  $n$ ), we split the computation into two parts: first, we compute the solution after advection,  $T^a$ , and use this result as input to a scheme that computes the diffusion. We begin by considering the advection scheme. Although it is possible to assemble and solve the system

$$\int_{\Omega} q \frac{\partial T}{\partial t} dX - \int_{\Omega} \nabla q \cdot \mathbf{u} T dX = 0, \quad (2.17)$$

which models the advection, this assembly will result in a matrix that is not symmetric positive-definite. Solving this system requires the use of a method such as GMRES; however, there are no efficient CUDA implementations of this method freely available, so we are restricted to making use of the CUDA Conjugate Gradient solver [Markall and Kelly, 2009]. In order to work around this problem, we use an explicit time-stepping scheme, the Runge-Kutta method [Weisstein, 2009]. Using a fourth-order Runge-Kutta scheme to integrate  $T$  with respect to time leads to the following systems of equations:

$$\int_{\Omega} q T_1 dX = -\Delta t \int_{\Omega} \nabla q \cdot \mathbf{u}^n T^n dX \quad (2.18)$$

$$\int_{\Omega} q T_2 dX = -\Delta t \int_{\Omega} \nabla q \cdot \mathbf{u}^{n+\frac{1}{2}} (T^n + \frac{1}{2} T_1) dX \quad (2.19)$$

$$\int_{\Omega} q T_3 dX = -\Delta t \int_{\Omega} \nabla q \cdot \mathbf{u}^{n+\frac{1}{2}} (T^n + \frac{1}{2} T_2) dX \quad (2.20)$$

$$\int_{\Omega} q T_4 dX = -\Delta t \int_{\Omega} \nabla q \cdot \mathbf{u}^{n+1} (T^n + T_3) dX \quad (2.21)$$

$$\int_{\Omega} q T^a dX = \int_{\Omega} q T^n dX + \frac{1}{6} T_1 + \frac{1}{3} T_2 + \frac{1}{3} T_3 + \frac{1}{6} T_4 \quad (2.22)$$

where  $T^n$  is the tracer concentration at the beginning of the timestep,  $T^a$  is the tracer concentration at the end of the advection step, and  $\mathbf{u}^n$ ,  $\mathbf{u}^{n+\frac{1}{2}}$  and  $\mathbf{u}^{n+1}$  are the velocity at the beginning, middle and end of the advection step. In the `test_advection_diffusion` program, the velocity at a point is constant with time. In practice, this means that  $\mathbf{u}^n = \mathbf{u}^{n+\frac{1}{2}} = \mathbf{u}^{n+1}$ . As in `test_laplacian`, order 1 basis functions are used for the finite element discretisation.

After the assembly and solution of these five systems of equations, we now use the solution  $T^a$  as input to the diffusion scheme. The diffusion step may be solved implicitly since the assembly of this system does result in a symmetric positive definite matrix. For this step, we assemble and solve the system:

$$\int_{\Omega} q T^{n+1} dX = \int_{\Omega} q T^a dX - \frac{1}{2} \left( \int_{\Omega} \nabla q \cdot \bar{\mu} \cdot \nabla T^a dX + \int_{\Omega} \nabla q \cdot \bar{\mu} \cdot \nabla T^{n+1} dX \right) \quad (2.23)$$

giving the solution  $T^{n+1}$ . Having found the solution for  $T^{n+1}$ , the entire process may be used to compute  $T^{n+2}$  and so on, until the solution at the desired timestep is reached.

## 2.5 The Unified Form Language

The *Unified Form Language*, or UFL [Alnaes and Logg, 2009a], originated from the research conducted as part of the FEniCS project [Dupont *et al.*, 2003, Logg, 2007]. In order to introduce the language, we must first introduce the notion of linear and bilinear forms. For example, we might introduce the notation

$$a(v, u) = \int_{\Omega} \nabla v \cdot \nabla u dX \quad (2.24)$$

and we refer to  $a$  as a *bilinear form*, so called as it is linear in both its arguments. A linear form takes a single argument in which it is linear. As we have seen in previous sections, use of the finite element method requires the evaluation of linear and bilinear forms as in Equation 2.24, the results of which produce local matrices which are summed into the global matrix. UFL is a domain-specific language that provides the programmer with a convenient notation to express these forms, without requiring any particular details about how to implement the evaluation of these forms to be specified. The UFL compiler outputs code to evaluate these forms and perform the global assembly, freeing the programmer from the tedious and error-prone process of writing it by hand.

We will introduce the language with a small example, which specifies the assembly of the first term in Equation 2.11. The following UFL code expresses the evaluation of the form  $a$  (which we note represents the term of interest) with test and trial functions  $v$  and  $u$  as follows:

```

psi=FunctionSpace(mesh, "CG", 1)

v=TestFunction(psi)

u=TrialFunction(psi)

A=-dot(grad(v), grad(u))*dx

```

The statement `psi=FunctionSpace(mesh, "CG", 1)` specifies that `psi` is a function space defined over some mesh (how the mesh `mesh` is obtained is not discussed in this example). The parameters "`CG`", `1` tell the UFL compiler that the basis functions of the functional space are piecewise continuous polynomials of order 1, as defined in Equation 2.6. `v=TestFunction(psi)` and `u=TrialFunction(psi)` specify that `v` is a test function and `u` is a trial function, which are both defined on the same mesh as `psi`. The final line specifies that the matrix `A` is assembled from the form in Equation 2.24.

One of the main advantages of using UFL to specify a finite element method is that a UFL specification describes the mathematical operations from a high level without describing how these operators are implemented. Since the implementation of the method is left to the UFL compiler, the user of UFL does not have to worry about the specifics of the implementation which would have to be considered when using a lower-level language such as Fortran or C++. A UFL compiler targeting a particular architecture may be tuned to generate code which is optimised for the specific performance characteristics of the that architecture.

### 2.5.1 UFL Compiler Optimisations

As a UFL Compiler is given a declarative specification rather than an imperative one, it is free to make choices about how the generated code should implement the specification in order to optimise performance. We shall consider an example of one of the choices the compiler may make. It is not always efficient to assemble a matrix whenever the assignment of a bilinear form is encountered. The optimal choice depends on how the resulting matrix is subsequently used. For example, consider a portion of the assembly of the diffusion scheme described in Equation 2.23:

```

M=p*q*dx

rhs=action(M+0.5*d, t)

A=M-0.5*d

```

In this example the matrix `M` is not used as a matrix of coefficients in a solve (though this is not evident from the above code), but is only used as an intermediary matrix for the construction of the matrix `A`, and the right-hand side vector. Assembling a full sparse matrix for `M` will be very costly in terms of memory usage, and possibly in terms of computation required to construct the matrix sparsity pattern.

Since `M` is not directly required, an efficient schedule for executing this code may consist of fusing the loops that assemble the right-hand side vector and the matrix. After this optimisation, the elemental submatrices that make up the matrix `M` may be assembled for each element in the mesh at each iteration of the loop - this elemental submatrix may then be used to compute `M`'s action on the elemental sub-vector that contributes to the right-hand side vector, and also added into the elemental submatrix calculation for `A`. At the end of an iteration of the loop, the elemental submatrix of `M` is no longer required, and is freed. This scheme also avoids a *Sparse Matrix-Vector* (SpMV) product being computed for a very large sparse matrix, replacing it with many small, dense matrix-vector multiplications.

Whether it is more efficient to fully assemble `M` or to only ever assemble its elemental submatrices may not be determined from simply examining the two possibilities, but is instead dependent upon the target architecture. In this example we seek not to demonstrate which algorithm is better, but that there is an optimisation space to be explored, and further that the user of UFL need not consider this optimisation space.

## 2.6 Summary

We have examined the NVidia Tesla Architecture and CUDA programming language, and it has been seen that performance optimisation of CUDA code is time-consuming and error-prone. The finite element method has been discussed in brief, and we have seen that it is a very flexible method, but its implementation is complex as it consists of many steps. The Fluidity code has

been introduced, and we have described the two test problems that we focus on throughout this report. Finally, we have introduced the UFL language, which allows finite element methods to be specified at a high level, and isolates the description of a method from its low-level implementation.

# Chapter 3

## Related Work

### 3.1 Introduction

In this chapter we seek to examine and evaluate work related to that conducted as part of this project. We draw on research in the following areas:

**Recent developments in the implementation of finite element assembly on GPU hardware.** The application of these methods includes the simulation of hyperelastic materials, the implementation of the Discontinuous Galerkin method to solve electromagnetic scattering problems, soft tissue modelling for surgical simulation, and modelling of seismic waves in earthquakes.

**Generative programming.** We describe the Tensor Contraction Engine and the motivation for its creation. We examine PyCUDA, a tool that may be used to automate the exploration of the optimisation space of CUDA kernels. Finally, we describe the work on automation and code generation of finite element methods, focusing particularly on the FEniCS project.

### 3.2 Finite Element Assembly on GPUs

#### 3.2.1 The Genesis of the Finite Element Method on Graphics Processors

The first implementation of the finite element method using graphics processing hardware was presented in [Rumpf and Strzodka, 2001], which implemented a nonlinear diffusion scheme. At the time at which this work was done, graphics hardware was not designed with general purpose computation in mind. In order to overcome the limitations of the hardware, mathematical operators had to be encoded as operations on textures. Due to the hardware limitations in the early graphics hardware, the implementation presented was slower than an equivalent CPU implementation executed on an SGI Onyx2 with 4 195MHz R10000 processors.

Since modern GPUs are far more powerful than the hardware used in this study, and have general purpose programming interfaces, the technical contributions of this work are largely unrelated to current techniques for the implementation of the finite element method on GPUs. We shall see in the following subsections that performance improvements may be obtained when using modern GPUs for finite element assembly.

#### 3.2.2 Hyperelastic Material Simulation

It has recently shown that finite element assembly of the system of equations for the modelling of a hyperelastic material [Ogden, 1997] can yield speedups of up to 15 times over a CPU implementation [Filipovic *et al.*, 2009a, Filipovic *et al.*, 2009b]. In this work, an implementation of the assembly of equations modelling a St. Venant-Kirchhoff material using an NVidia 280GTX GPU is presented. The authors identify that the operations which make up the assembly process are massively parallel (since each element-local matrix may be computed in independently) but the

granularity of these operations does not have an ideal mapping on to the NVidia Tesla architecture. The operations are referred to as *medium-grained*, since they are too large to be efficiently computed by a single thread, but too small to be efficiently computed by an entire thread block.

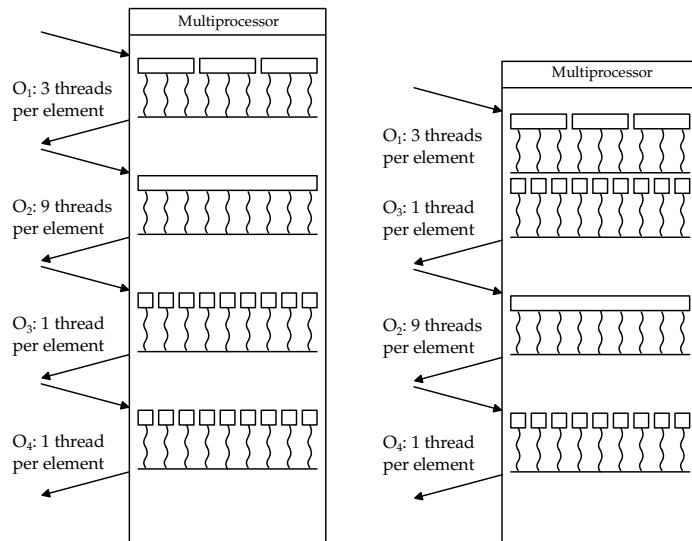

In order to implement these medium grained operations, an implementation is described in which small numbers of threads perform an algebraic operation for an element in parallel and store the intermediate result into shared memory. The use of separate kernels for each mathematical operator allows the programmer to increase efficiency by choosing the optimum number of threads to compute a result for each element on a per-operator basis. However, the negative side-effect of this approach is that the implementation quickly becomes memory bandwidth-limited, as a large number of intermediate values need to be passed between each kernel through global memory.

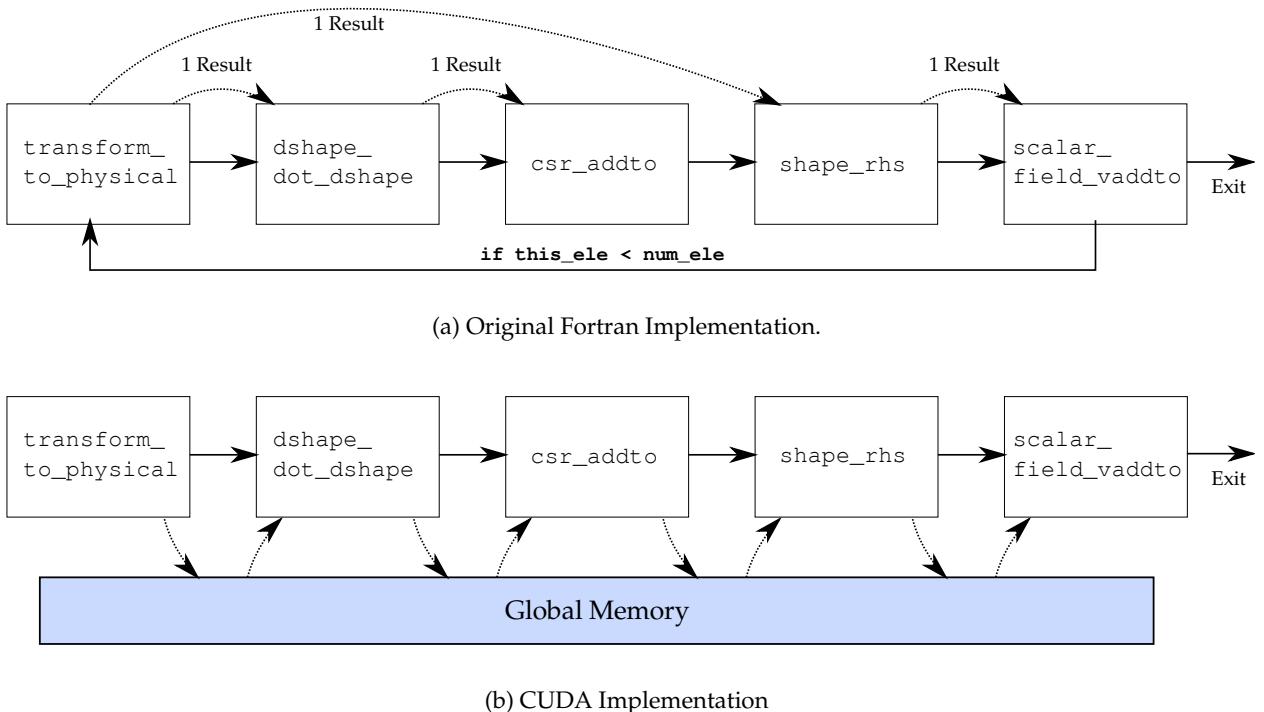

A proposed solution to overcome this bottleneck involves fusing kernels and passing intermediate results in shared memory. This results in a performance gain as the pressure on the memory bandwidth is reduced. An example of this optimisation is shown in Figure 3.1. On the left, the unmodified kernels pass data through global memory. The output of kernel  $O_1$  is stored in global memory and read by kernel  $O_3$ . To create the right-hand implementation, these two kernels are fused and the output from  $O_1$  is stored in shared memory, which is read back by the portion of the new kernel that performs the operation  $O_3$ .

The example shows that fused kernels may have used different numbers of threads to compute the result for a single element. This can lead to inefficiency as in the fused kernel, some of the threads will be idle whilst the reduced number of threads computes the work of one of the original kernels. As a result, some kernel fusions may result in less efficient code than that which executes each operation in a separate kernel and passes intermediate results through global memory.

Figure 3.1: Left: Individual kernels exchange data in global memory. Right: Fused kernels exchange data through global memory. From [Filipovic *et al.*, 2009b]

When performing kernel fusions, there are also other tradeoffs that must be made to produce the most efficient implementation. It may be expected that increasing the number of operations performed by one kernel should result in an increase in speed due to the reduced memory bandwidth requirement. However, as the size of a kernel increases, its use of registers and shared memory also increases. This decreases the occupancy of the kernel, which can have a negative impact on performance. Secondly, the order in which operations are composed whilst remaining semantically equivalent has an effect on the resource usage of kernels. This design space must also be explored in the search for optimal performance. Although the authors do not discuss the automated exploration of these optimisation spaces, we observe that manual exploration is a time-consuming and error-prone process, unlikely to discover the optimum with a reasonable amount of effort.

The performance results presented by the authors show that the GPU accelerated implementation gives a speedup of 15 times over the CPU implementation when using an NVidia 280GTX GPU and and Intel Core2 Quad Q9550 with 8GB RAM. The performance improvement from fusing kernels yields a further improvement of 1.8 times over the unfused kernels. Unfortunately the authors do not report the compilers they used, or even whether computations are performed in single or double precision. Furthermore, the speedups presented are over a single core - benchmarking the CPU implementation using multiple cores would provide a more representative baseline against which the GPU implementation may be evaluated.

In conclusion, it is clear that increased performance may be obtained by using GPUs for finite element assembly, though the magnitude of this performance increase is unclear. Ideal mapping of the assembly algorithms on to the GPU hardware may be achieved by a careful choice of the number of threads per element for each operation. Optimisation of a GPU implementation will require testing the fusion of different combination of kernels, a task which ideally would be performed by an optimising compiler.

### 3.2.3 Discontinuous Galerkin on GPUs

*Discontinuous Galerkin* (DG) methods [Donea, 2003] are a class of finite element methods in which the majority of computation is applied locally to each element, and a *flux function* couples neighbouring elements. This structure of the method maps well on to a GPU architecture, since it has a high ratio of computation to data, and each element may be processed individually for most operations. The method has been implemented on the NVidia Tesla architecture and benchmarked against a CPU implementation [Klöckner *et al.*, 2009].

#### The DG Method

We shall briefly summarise the DG method presented in the paper, which solves a linear hyperbolic system of conservation laws:

$$\frac{\partial u}{\partial t} + \nabla \cdot F(u) = 0 \quad (3.1)$$

where  $F$  is the flux function. The system is solved on a 3D mesh of tetrahedral elements by timestepping the discrete equation

$$\frac{\partial u}{\partial t} = - \sum_{\nu} D^{k,\partial\nu} [F(u^k)] + L^k [\hat{n} \cdot F - (\hat{n} \cdot F)^*]|_{A \subset \partial D_k} \quad (3.2)$$

where  $\nu$  is the set of elements,  $u^k$  is the values of  $u$  on the element  $k$ ,  $\hat{n}$  is the outward pointing unit normal on the element face,  $(\hat{n} \cdot F)^*$  is some numerical flux in the normal direction, and  $D_k$  is the domain of element  $k$ . The Differentiation and Lifting matrices,  $D^{k,\partial\nu}$  and  $L^k$  are defined by

$$M_{ij}^k = \int_{D_k} \Phi_i \Phi_j dX \quad (\text{Mass})$$

$$S_{ij}^{k,\partial\nu} = \int_{D_k} \Phi_i \partial_{x_\nu} \Phi_j dX \quad (\text{Stiffness})$$

$$M_{ij}^{k,A} = \int_{A \subset \partial D_k} \Phi_i \Phi_j ds \quad (\text{Face Mass})$$

$$D^{k,\partial\nu} = (M^k)^{-1} S^{k,\partial\nu} \quad (\text{Differentiation})$$

$$L^k = (M^k)^{-1} M^{k,A} \quad (\text{Lifting})$$

The DG method may be decomposed into four stages:

**Flux Gather.** This involves computation of the term  $[\hat{n} \cdot F - (\hat{n} \cdot F)^*]|_{A \subset \partial D_k}$ . This is the only operation in which the computation is not purely element-local.

**Flux Lifting.** This involves the computation of the element-local Lifting matrix  $L^k$  and its action on the term computed in the Flux Gather stage.

**Flux Evaluation.** This is the evaluation of the Flux function  $F(u^k)$  on each element  $k$ .

**Local Differentiation.** This stage involves computation of the local differentiation matrix  $D^{k,\partial\nu}$  and its action on the Flux function computed in the Flux Evaluation stage.

The results of the Flux Lifting and Local Differentiation stages are summed into the matrix  $A$  (as in Equation 2.7). Since the all nodes are only local to a single element, the structure of the resulting matrix is blockwise diagonal with no coupling between blocks [Donea, 2003, p.125]. This makes the matrix very easy to invert, and this process may be done on an elementwise basis.

## GPU Implementation and Optimisation

The implementation of the method is mapped on to the GPU as four kernels, each corresponding to one of the stages described in the previous subsection. We briefly outline some of the design decisions and optimisations described in the publication, and avoid a restatement of the entire description of the implementation.

It is stated that using the shared memory for storing element-local matrices leads to inefficiency since it is too small to store matrices for a large number of elements. In the case of tetrahedral elements with order 1 basis functions, each local matrix is a  $4 \times 4$  matrix. The storage of one matrix in single precision requires 64 bytes, so up to 256 element-local matrices may be stored on the shared memory of one SM. Assuming one thread computes the output for a single element, this allows 256 threads to occupy a single SM. This is a reasonable level of occupancy; however, for the higher-order basis functions used in this implementation, the matrices quickly become too large. For example, a tetrahedron with order-4 basis functions has 35 degrees of freedom, so the local matrix is  $35 \times 35$ . In this case, each local matrix element requires 4900 bytes of shared memory, permitting the storage of only 3 element-local matrices in the shared memory of one SM.

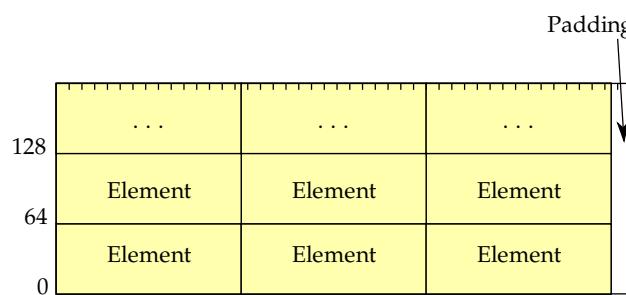

Since the nodal data only requires a small amount of data for each element, the authors decided that it may efficiently be prefetched into shared memory at the beginning of kernel execution, and copying results back to main memory after computation has been performed. As the length (in bytes) of element data for a single element is often not a factor of 16 or 32 (the size of a half-warp and warp respectively), consecutive elements are placed adjacently in memory until their combined length is close to 64 bytes, and padding is added. See Figure 3.2 for an example of this layout. This layout allows coalesced accesses to be made when prefetching the data into shared memory, whilst wasting a minimal amount of memory space and bandwidth.

Figure 3.2: Padding of packed multiple elements to 64 bytes. From [Klöckner *et al.*, 2009].

The authors explore the idea of fusing kernels. For example, the Gather and Lifting kernels may be candidates for fusion since the output of the Gather stage is the input to the Lifting stage. However, it is concluded that this would lead to inefficient kernels, since different numbers of threads are used to compute each output value in the two kernels, leading to some threads idling for a portion of the fused kernel execution. This is in contrast to the results presented in

[Filipovic *et al.*, 2009a], where an increase in speed is reported even when kernels which use different numbers of threads per output are fused. We conclude that fusion of kernels should be explored when optimising a CUDA implementation of the finite element method, since it may lead to increased performance in some cases. However, in other cases it may be detrimental to performance.

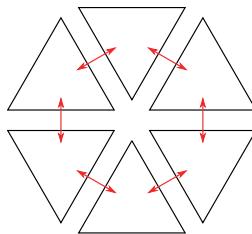

The Flux Gather stage requires flux data to be fetched for each face of each element. Since neighbouring elements share a face, the data for each face is required to be loaded from global memory twice (see Figure 3.3). In order to reduce the memory bandwidth usage, a partitioning scheme is used where small partitions of elements are created using a greedy algorithm. In the Gather kernel, an entire partition is prefetched into shared memory before computation is performed. As a result of this optimisation, data for faces on the interior of the partition are only transferred once.

Figure 3.3: Flux between neighbouring elements.

Other optimisations that were explored include loop unrolling and constant folding, and using the texture cache to access the lifting matrix, as an alternative to using shared memory. The exploration of some of these optimisations was facilitated by using the metaprogramming system in PyCUDA (see Section 3.4).

## Performance Results and Conclusions

Benchmarking of the implementation is performed using an NVidia 280GTX GPU and a single core of an Intel Core 2 Duo E8400, both operating in single precision. The test problem is an electromagnetic scattering problem, which involves finding solutions to Maxwell's Equations [Monk, 2003]. A speedup of between 24 and 57 times is shown, depending on the order of the method used. These speedups appear impressive - however, the compiler and flags used for the CPU implementation are not mentioned, and we may suspect that the CPU implementation is running sub-optimally. Additionally, benchmarking using a single core of a CPU does not provide a representative baseline to compare against, since modern CPUs have up to eight cores.

In conclusion, we have seen that the DG method is amenable to speedup using GPUs, and may form part of our further investigations into the implementation of the finite element method on GPUs. Since the optimisations that were reported to have a beneficial effect on performance differ from those described in the previous section, we conclude that optimising the implementation of finite element methods on GPUs requires a careful choice of techniques, and that there is no clear strategy for determining which optimisations may be the most worthwhile to implement. Instead, experimentation must be performed to determine which optimisations result in performance improvements for a given implementation.

### 3.2.4 Soft Tissue Modelling in the SOFA Framework

The *Total Lagrangian Explicit Dynamics* (TLED) method [Miller *et al.*, 2007] is a finite element method designed for modelling soft tissue for surgical simulations. The execution of the algorithm consists of two main loops. The first loop iterates over each element in the mesh to compute stress and strain forces, and the second loop iterates over nodes in the mesh, computing their new positions based on these forces. This algorithm differs from the formulation of the finite element

method described in Section 2.3, which consists of an assembly phase and a solver phase. However, the computation of the stress and strain forces is a similar process to the assembly phase. A full explanation of the TLED method is outside the scope of this report.

The first implementation of the TLED method was written in the NVidia Cg [NVidia, 2009b] language [Taylor *et al.*, 2008, Taylor *et al.*, 2007], and executed on older GPU architectures, before the availability of the Tesla architecture and CUDA. This implementation showed speedups of 16.4 times over the CPU for a model problem, and up to 14 times for a more realistic model of displacements in a model brain.

## The SOFA Framework

A subsequently-developed implementation of this algorithm was produced using the *Simulation Open Framework Architecture* (SOFA) [Allard *et al.*, 2007]. SOFA is a framework designed to facilitate the development of real-time simulations, in particular medical simulations. A complete simulation is produced by composing individual behaviour models that contribute to different aspects of the simulation. For example, one may combine a collision model, a visual model and a haptic model to produce a simulation of a surgical procedure.

Each modelling area is further subdivided in a domain-specific decomposition. We focus on the behaviour model, which is used to simulate the physical motion of tissue, and has the following subdivisions: Degrees of Freedom, Mass, Force Field, and Solver. A component from each of these divisions is selected in order to construct a complete behaviour model. Implementing a new biomechanical model (such as the TLED method) requires a new Force Field module to be developed in C++. The framework provides the programmer with a relatively high-level interface to assist the development of their model, but it does not provide any abstractions from implementation in the C++ language.

Implementation of the TLED method using SOFA and CUDA is described in [Comas *et al.*, 2008]. Use of the CUDA language instead of Cg facilitated the use of shared memory and the texture cache to improve performance, though the specific details of optimisations are omitted. Pinned memory is used to increase the data transfer speed to the GPU.

## Performance Results

Benchmarking the SOFA implementation using a GeForce 8800GTX GPU shows a speedup of up to 53.6 times over the CPU implementation on an Intel Core 2 Duo 2.4GHz when using single precision arithmetic. Unfortunately the compiler used for the CPU implementation is not reported, nor is the number of cores used for the simulation. We may suspect that a single core was used to execute the CPU implementation. A speedup of 37 times for a simulation of an eye in cataract surgery is reported. The accuracy of the simulation compared to the CPU is not discussed - although some discrepancy is likely due to differences in the implementation of floating point calculations, whether the solutions are qualitatively equivalent is not mentioned.

In order to demonstrate that the overhead of using the SOFA framework is very low, the TLED algorithm is implemented as a standalone program. The execution time of the standalone program is compared to the SOFA implementation for a test problem. It is shown that the use of SOFA adds an overhead of approximately 8.4%, which is considered to be an acceptable increase due to the ease of integration with other models which the SOFA framework permits.

## Conclusion

We may conclude that the provision of a framework in which finite element methods may be developed and composed with other models increases the ease with which they may be implemented. However, this does not provide portability to other architectures, since the C++ code which implements the Force Field for TLED makes calls to CUDA kernels. Additionally, making changes to an algorithm implemented using C++ and CUDA will require a non-trivial effort, since the algorithm is entwined with its implementation.

### 3.2.5 High-Order Earthquake Modelling

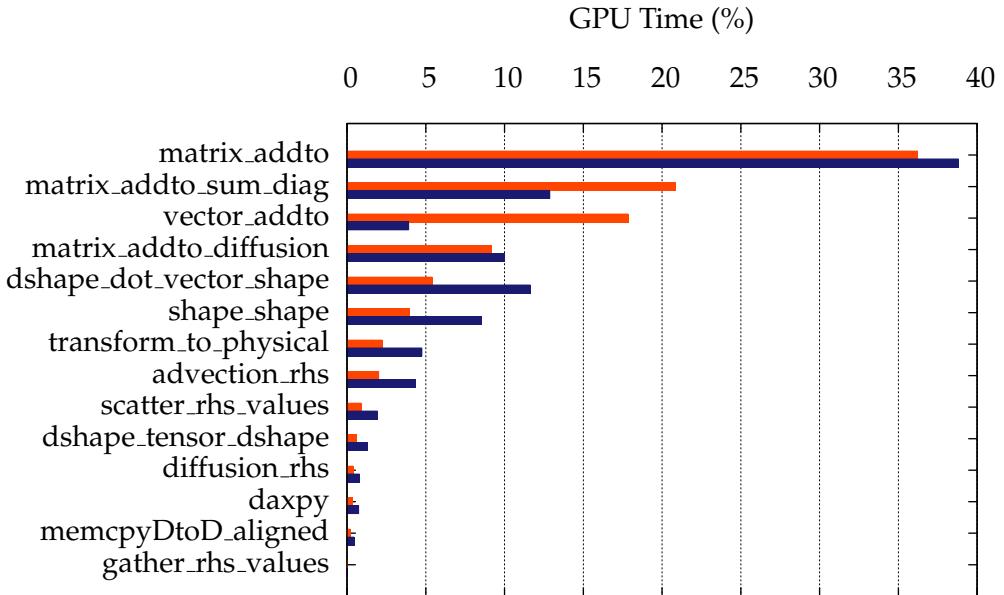

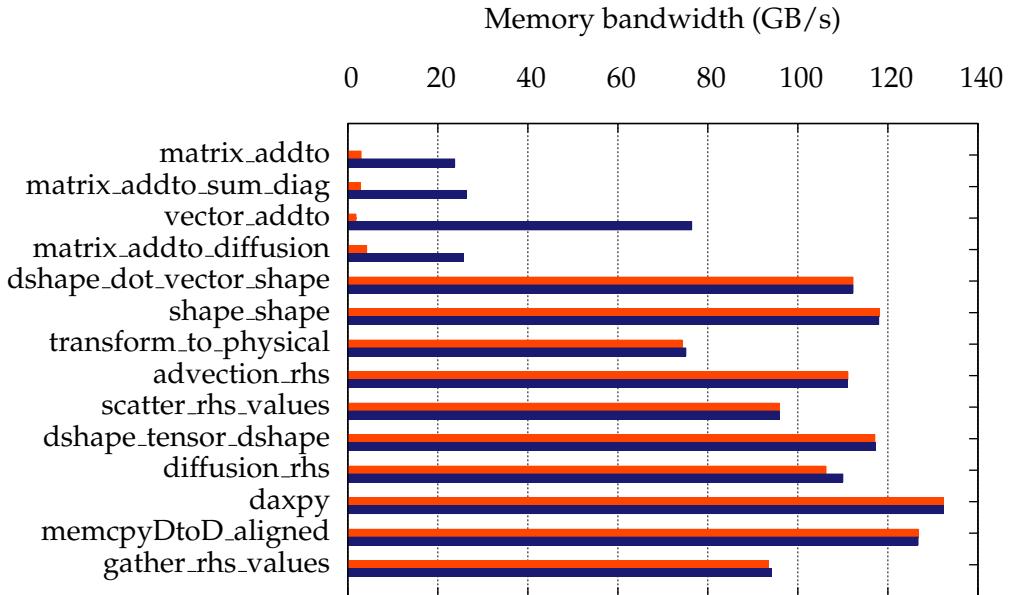

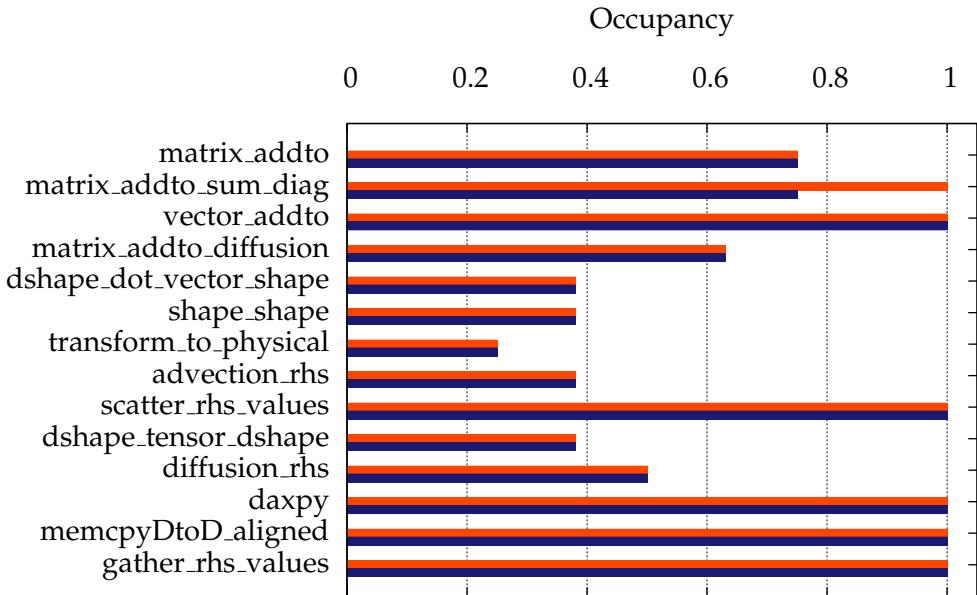

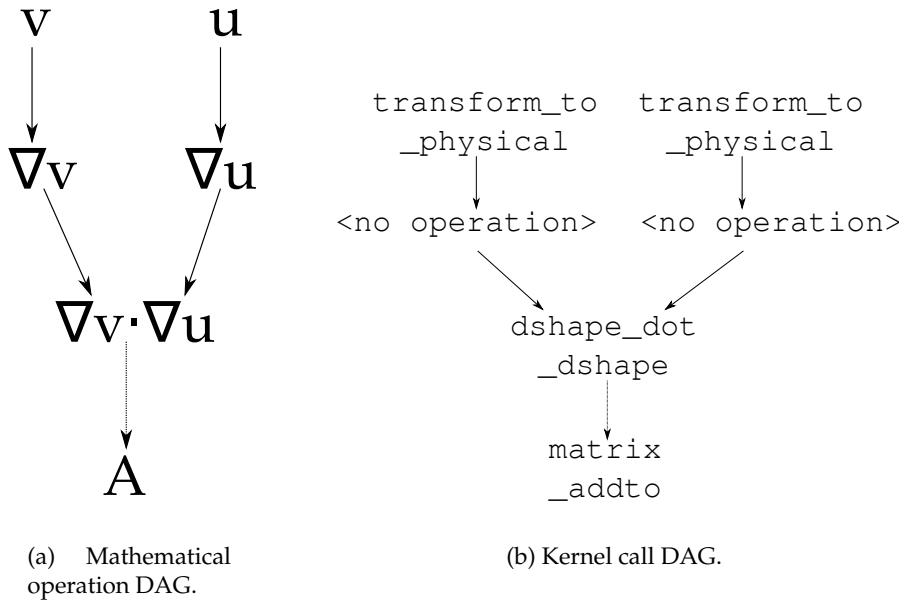

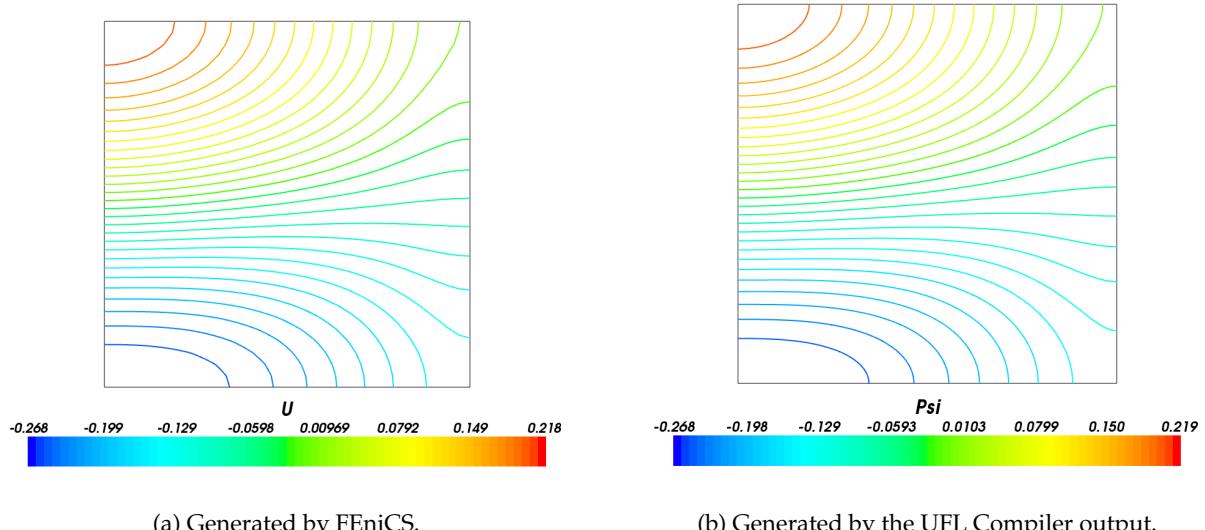

[Komatitsch *et al.*, 2009] describes the implementation of a finite element earthquake model using CUDA. We do not repeat all the optimisations described, as most of them are similar to those already examined in previous sections. Rather, we shall describe an optimisation that we have not previously discussed, involving a colouring of the elements to increase the efficiency of the assembly phase.